## **МИКРОСХЕМА ИНТЕГРАЛЬНАЯ 1892ВМ3Т**

**Руководство пользователя**

## Перечень сокращений:

- **CPU** – центральный процессор на основе RISC-ядра;

- **CRAM** – двухпортовая оперативная память центрального процессора;

- **DSP** – сопроцессор цифровой обработки сигналов с фиксированной точкой (далее может называться также **ЦПОС** – цифровой процессор обработки сигналов);

- **DMA** – контроллер прямого доступа в память;

- **MPORT** – порт внешней памяти;

- **SPORT** – последовательный порт;

- **LPORT** – линковый порт;

- **UART** – универсальный асинхронный порт;

- **ICACHE** – кэш программ центрального процессора;

- **IT** – интервальный таймер;

- **WDT** – сторожевой таймер;

- **RTT** – таймер реального времени;

- **CDB[31:0]** – шина данных CPU;

- **DDB[31:0]** – шина данных DMA;

- **A[31:0]** – шина адреса порта внешней памяти;

- **D[31:0]** – шина данных порта внешней памяти;

- **OnCD** – встроенные средства отладки программ;

- **XRAM, YRAM** – памяти данных DSP;

- **PRAM** – память программ DSP;

- **AGU** – адресный генератор;

- **EDBS** – коммутатор внешних шин;

- **IDBS** – коммутатор внутренних шин;

- **PCU** – устройство программного управления;

- **PAG** – генератор адреса программ;

- **PDC** – программный дешифратор;

- **RF** – регистровый файл;

- **ALU** – арифметическое устройство;

- **ALUCtr** – управление ALU;

- **XDB0 – XDB3, GDB, PDB** – шина данных DSP;

- **XAB, YAB, PAB** – адресные шины DSP;

- **M, S, A, L** – арифметические узлы ALU DSP.

## Содержание документа

|                                                                                                |    |

|------------------------------------------------------------------------------------------------|----|

| СОДЕРЖАНИЕ ДОКУМЕНТА .....                                                                     | 3  |

| 1. ВВЕДЕНИЕ .....                                                                              | 10 |

| 1.1 ПОРЯДОК ИСПОЛЬЗОВАНИЯ ДАННОГО ДОКУМЕНТА .....                                              | 10 |

| 1.2 НАЗНАЧЕНИЕ .....                                                                           | 11 |

| 1.3 ФУНКЦИОНАЛЬНЫЕ ПАРАМЕТРЫ И ВОЗМОЖНОСТИ .....                                               | 12 |

| 1.4 СТРУКТУРНАЯ СХЕМА .....                                                                    | 17 |

| 1.5 ИНСТРУМЕНТАЛЬНОЕ ПРОГРАММНОЕ ОБЕСПЕЧЕНИЕ .....                                             | 21 |

| <i>Интегрированная среда проектирования включает:</i> .....                                    | 21 |

| <i>Среда разработки программ для RISC – ядра включает:</i> .....                               | 21 |

| <i>Среда разработки программ для ЦПОС – ядра включает:</i> .....                               | 21 |

| 1.6 ОПЕРАЦИОННАЯ СИСТЕМА ДЛЯ МИКРОСХЕМЫ МС-12 .....                                            | 22 |

| 1.7 ДОПОЛНИТЕЛЬНАЯ ДОКУМЕНТАЦИЯ .....                                                          | 23 |

| 2. ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР .....                                                                 | 24 |

| 2.1 ОСНОВНЫЕ ХАРАКТЕРИСТИКИ CPU .....                                                          | 24 |

| 2.2 БЛОК СХЕМА .....                                                                           | 24 |

| 2.3 СОСТАВЛЯЮЩИЕ ЛОГИЧЕСКИЕ БЛОКИ .....                                                        | 25 |

| 2.3.1 Устройство исполнения .....                                                              | 25 |

| 2.3.2 Устройство умножения/деления (MDU) .....                                                 | 25 |

| 2.3.3 Системный управляющий сопроцессор .....                                                  | 25 |

| 2.3.4 Устройство управления памятью (MMU) .....                                                | 25 |

| 2.3.5 Контроллер кэш .....                                                                     | 26 |

| 2.3.6 Устройство шинного интерфейса (BIU – Bus Interface Unit) .....                           | 26 |

| 2.3.7 OnCD контроллер .....                                                                    | 26 |

| 2.4 КОНВЕЙЕР .....                                                                             | 26 |

| 2.4.1 Стадии конвейера .....                                                                   | 26 |

| 2.4.1.1 Стадия I: выборка команды .....                                                        | 27 |

| 2.4.1.2 Стадия D: дешифрация команды .....                                                     | 27 |

| 2.4.1.3 Стадия E: исполнение .....                                                             | 27 |

| 2.4.1.4 Стадия M: выборка из памяти .....                                                      | 28 |

| 2.4.1.5 Стадия W: обратная запись .....                                                        | 28 |

| 2.4.2 Операции умножения и деления .....                                                       | 28 |

| 2.4.3 Задержка выполнения команд перехода (Jump, Branch) .....                                 | 28 |

| 2.4.4 Обходные пути передачи данных (Data bypass) .....                                        | 28 |

| 2.4.5 Задержка загрузки данных .....                                                           | 29 |

| 2.5 УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ (MMU) .....                                                  | 30 |

| 2.5.1 Введение .....                                                                           | 30 |

| 2.5.2 Режимы работы .....                                                                      | 31 |

| 2.5.2.1 Виртуальные сегменты памяти .....                                                      | 31 |

| 2.5.2.2 Режим User .....                                                                       | 33 |

| 2.5.2.3 Режим Kernel .....                                                                     | 34 |

| 2.5.3 Буфер быстрого преобразования адреса (TLB) .....                                         | 37 |

| 2.5.4 Преобразование виртуального адреса в физический в режиме TLB .....                       | 40 |

| 2.5.4.1 Попадания (hits), промахи (misses), и множественные попадания (multiple matches) ..... | 41 |

| 2.5.4.2 Размеры страниц и алгоритм замещения .....                                             | 42 |

| 2.6 ИСКЛЮЧЕНИЯ .....                                                                           | 44 |

| 2.6.1 Условия исключений .....                                                                 | 44 |

| 2.6.2 Приоритеты исключений .....                                                              | 44 |

| 2.6.3 Расположение векторов исключений .....                                                   | 45 |

| 2.6.4 Обработка общих исключений .....                                                         | 46 |

|          |                                                                                                                                      |    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.6.5    | <i>Исключения</i>                                                                                                                    | 47 |

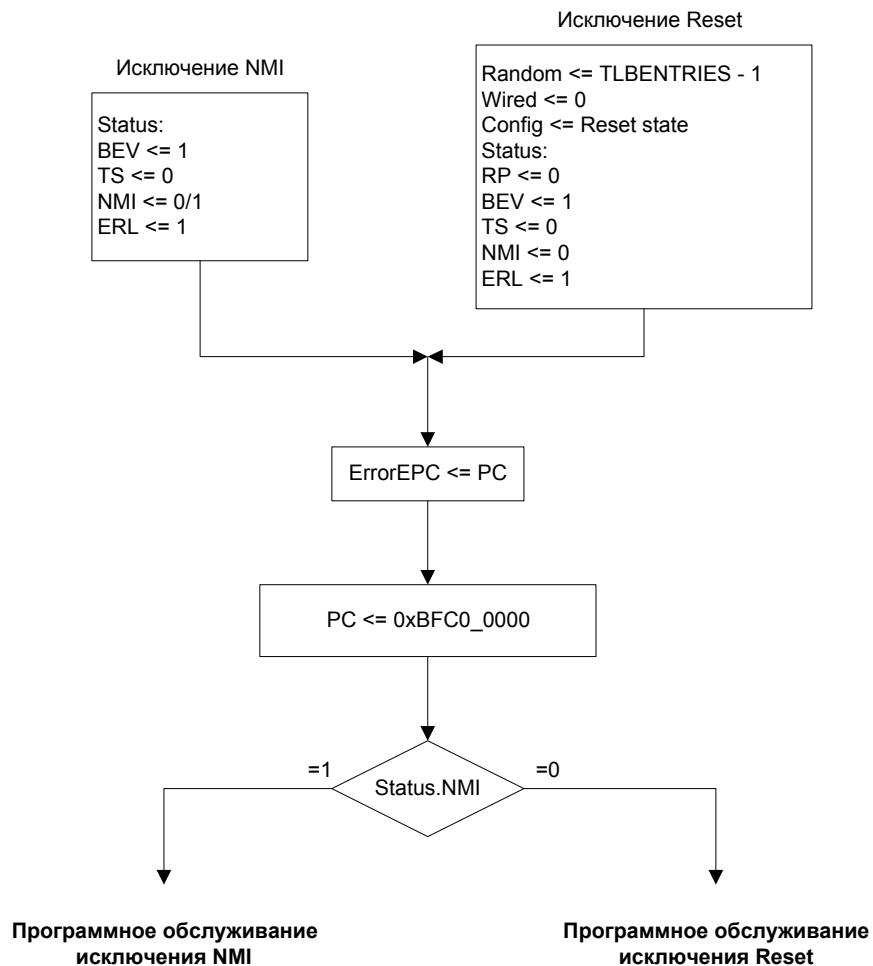

| 2.6.5.1  | Исключение по аппаратному сбросу (Reset Exception) .....                                                                             | 47 |

| 2.6.5.2  | Исключение по немаскируемому прерыванию (Non Maskable Interrupt - NMI Exception) .....                                               | 48 |

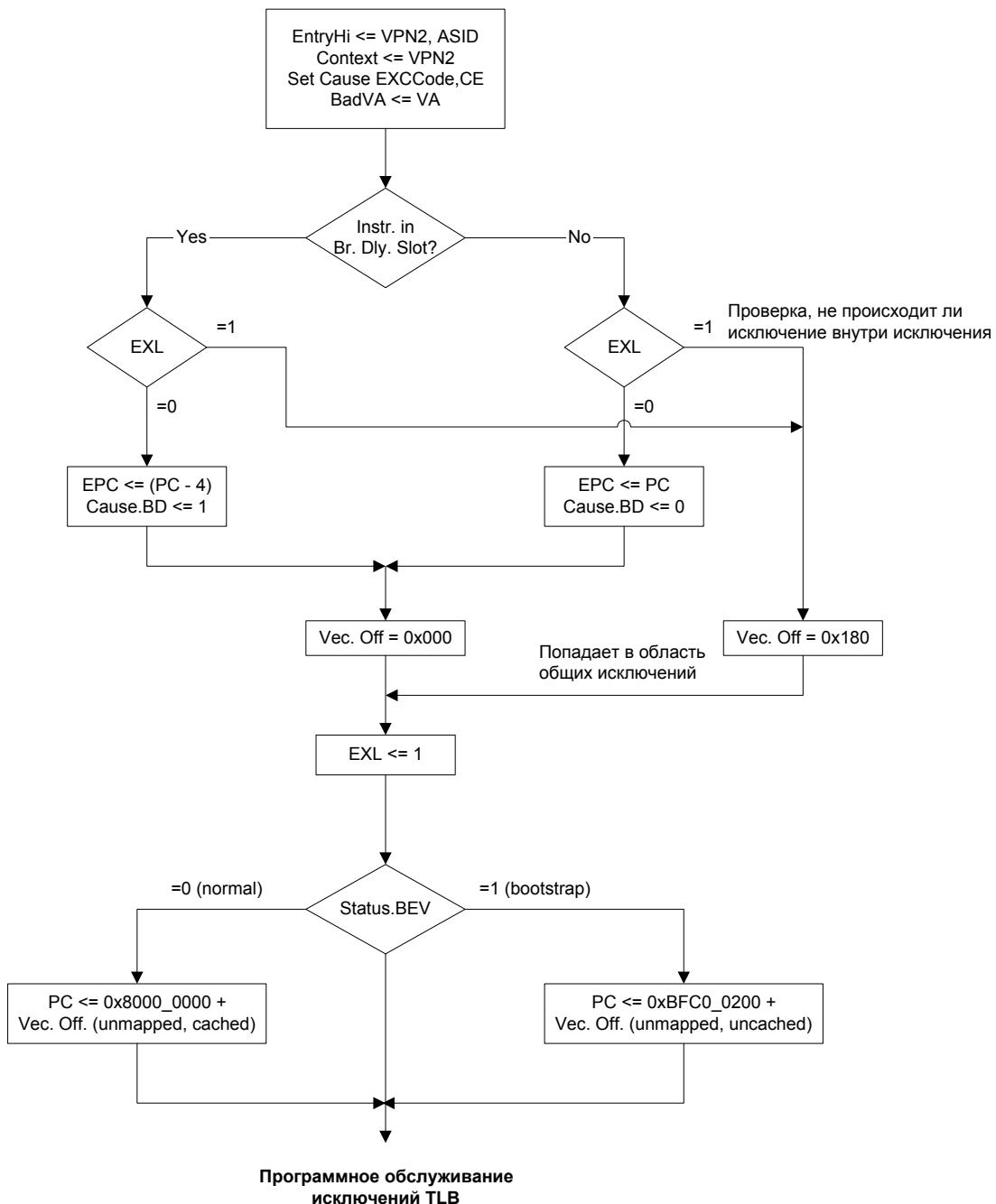

| 2.6.5.3  | Исключение по обновлению TLB – выборка команды или доступ к данным (TLB Refill Exception - Instruction Fetch or Data Access) .....   | 48 |

| 2.6.5.4  | Исключение TLB Invalid – выборка команды или доступ к данным (TLB Invalid Exception - Instruction Fetch or Data Access) .....        | 49 |

| 2.6.5.5  | Исключение по ошибке адресации – выборка команды / доступ к данным (Address Error Exception - Instruction Fetch / Data Access) ..... | 49 |

| 2.6.5.6  | Исключение по аппаратному контролю (Mcheck – Machine Check Exception) .....                                                          | 50 |

| 2.6.5.7  | Исключение исполнения – системный вызов (System Call Exception) .....                                                                | 50 |

| 2.6.5.8  | Исключение исполнения – Breakpoint (Execution Exception – Breakpoint) .....                                                          | 51 |

| 2.6.5.9  | Исключение исполнения – зарезервированная команда (Execution Exception – Reserved Instruction) .....                                 | 51 |

| 2.6.5.10 | Исключение исполнения – недоступен сопроцессор (Execution Exception – Coprocessor Unusable) .....                                    | 51 |

| 2.6.5.11 | Исключение исполнения – целочисленное переполнение (Execution Exception – Integer Overflow) .....                                    | 52 |

| 2.6.5.12 | Исключение исполнения – Trap (Execution Exception – Trap) .....                                                                      | 52 |

| 2.6.5.13 | Исключение сохранения в запрещенной области (TLB Modified Exception) .....                                                           | 52 |

| 2.6.5.14 | Исключение прерывания (Interrupt Exception) .....                                                                                    | 53 |

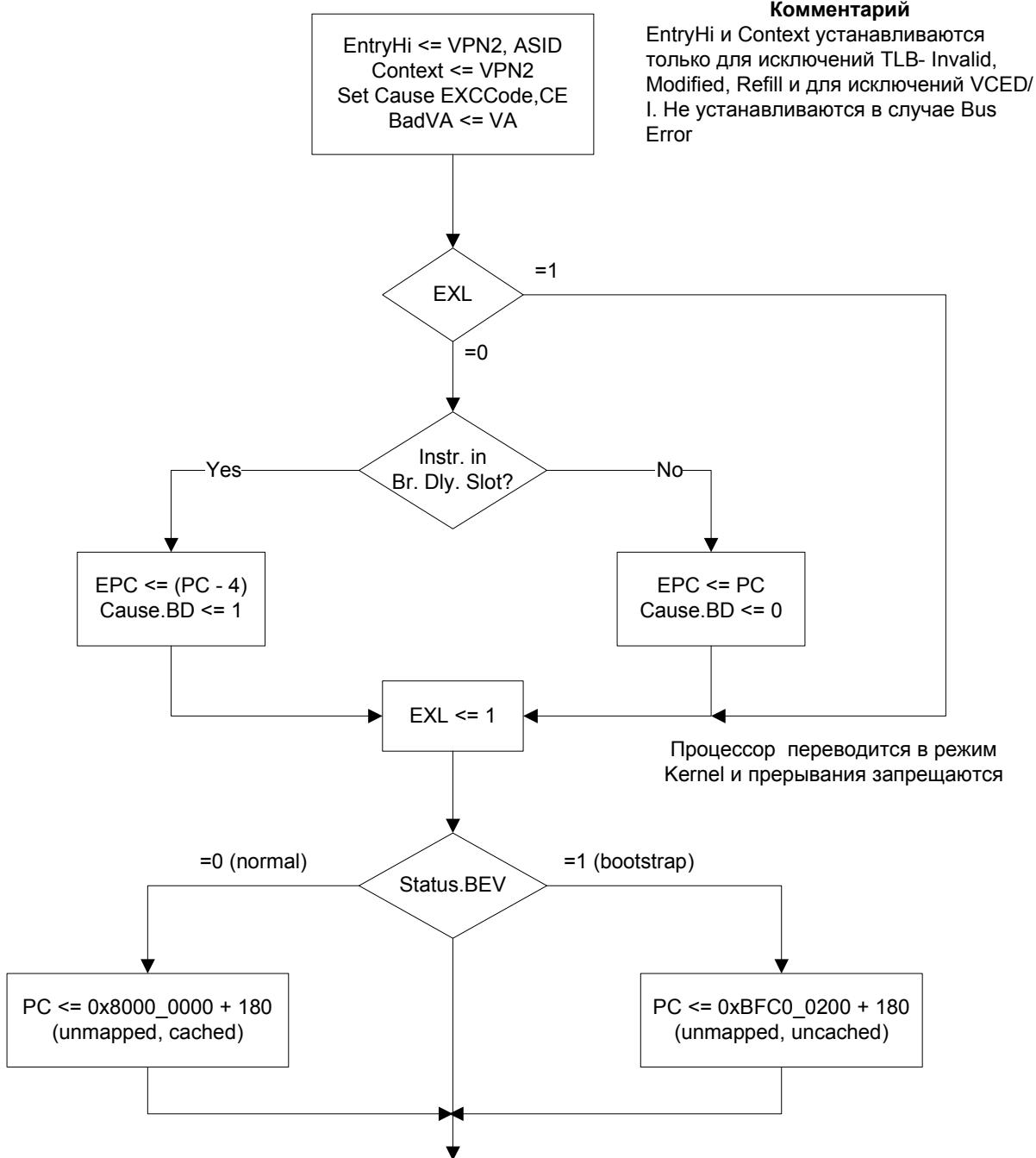

| 2.6.6    | <i>Алгоритмы обработки исключений</i> .....                                                                                          | 53 |

| 2.7      | <b>РЕГИСТРЫ СРО</b> .....                                                                                                            | 56 |

| 2.7.1    | <i>Назначение</i> .....                                                                                                              | 56 |

| 2.7.2    | <i>Обзор регистров CP0</i> .....                                                                                                     | 57 |

| 2.7.3    | <i>Регистры CP0</i> .....                                                                                                            | 58 |

| 2.7.3.1  | Регистр Random (Регистр CP0 1, Select 0) .....                                                                                       | 59 |

| 2.7.3.2  | EntryLo0, EntryLo1 (Регистры 2 и 3 CP0, Select 0) .....                                                                              | 59 |

| 2.7.3.3  | Регистр Context (Регистр 4 CP0, Select 0) .....                                                                                      | 60 |

| 2.7.3.4  | Регистр PageMask (Регистр 5 CP0, Select 0) .....                                                                                     | 61 |

| 2.7.3.5  | Регистр Wired (Регистр 6 CP0, Select 0) .....                                                                                        | 62 |

| 2.7.3.6  | Регистр BadVAddr (Регистр 8 CP0, Select 0) .....                                                                                     | 63 |

| 2.7.3.7  | Регистр Count (Регистр 9 CP0, Select 0) .....                                                                                        | 63 |

| 2.7.3.8  | Регистр EntryHi (Регистр 10 CP0, Select 0) .....                                                                                     | 64 |

| 2.7.3.9  | Регистр Compare (Регистр 11 CP0, Select 0) .....                                                                                     | 64 |

| 2.7.3.10 | Регистр Status (Регистр 12 CP0, Select 0) .....                                                                                      | 65 |

| 2.7.3.11 | Регистр Cause (Регистр 13 CP0, Select 0) .....                                                                                       | 68 |

| 2.7.3.12 | Регистр EPC (Регистр 14 CP0, Select 0) .....                                                                                         | 69 |

| 2.7.3.13 | Регистр PRId (Регистр 15 CP0, Select 0) .....                                                                                        | 70 |

| 2.7.3.14 | Регистр Config (Регистр 16 CP0, Select 0) .....                                                                                      | 70 |

| 2.7.3.15 | Регистр Config1 (Регистр 16 CP0, Select 1) .....                                                                                     | 71 |

| 2.7.3.16 | Регистр LLAddr – Load Linked Address (Регистр 17 CP0, Select 0) .....                                                                | 72 |

| 2.7.3.17 | Регистр ErrorEPC (Регистр 30 CP0, Select 0) .....                                                                                    | 72 |

| 2.8      | <b>Кэш</b> .....                                                                                                                     | 73 |

| 2.8.1    | <i>Введение</i> .....                                                                                                                | 73 |

| 2.8.2    | <i>Протокол кэши</i> .....                                                                                                           | 73 |

| 2.8.2.1  | Организация кэш .....                                                                                                                | 73 |

| 2.8.2.2  | Атрибуты кэшируемости .....                                                                                                          | 73 |

| 2.9      | <b>КАРТА ПАМЯТИ CPU</b> .....                                                                                                        | 74 |

| 3.       | <b>ЦИФРОВОЙ СИГНАЛЬНЫЙ ПРОЦЕССОР (DSP)</b> .....                                                                                     | 81 |

| 3.1      | ФУНКЦИОНАЛЬНЫЕ ПАРАМЕТРЫ И ВОЗМОЖНОСТИ DSP .....                                                                                     | 81 |

| 3.2      | АРХИТЕКТУРА DSP .....                                                                                                                | 82 |

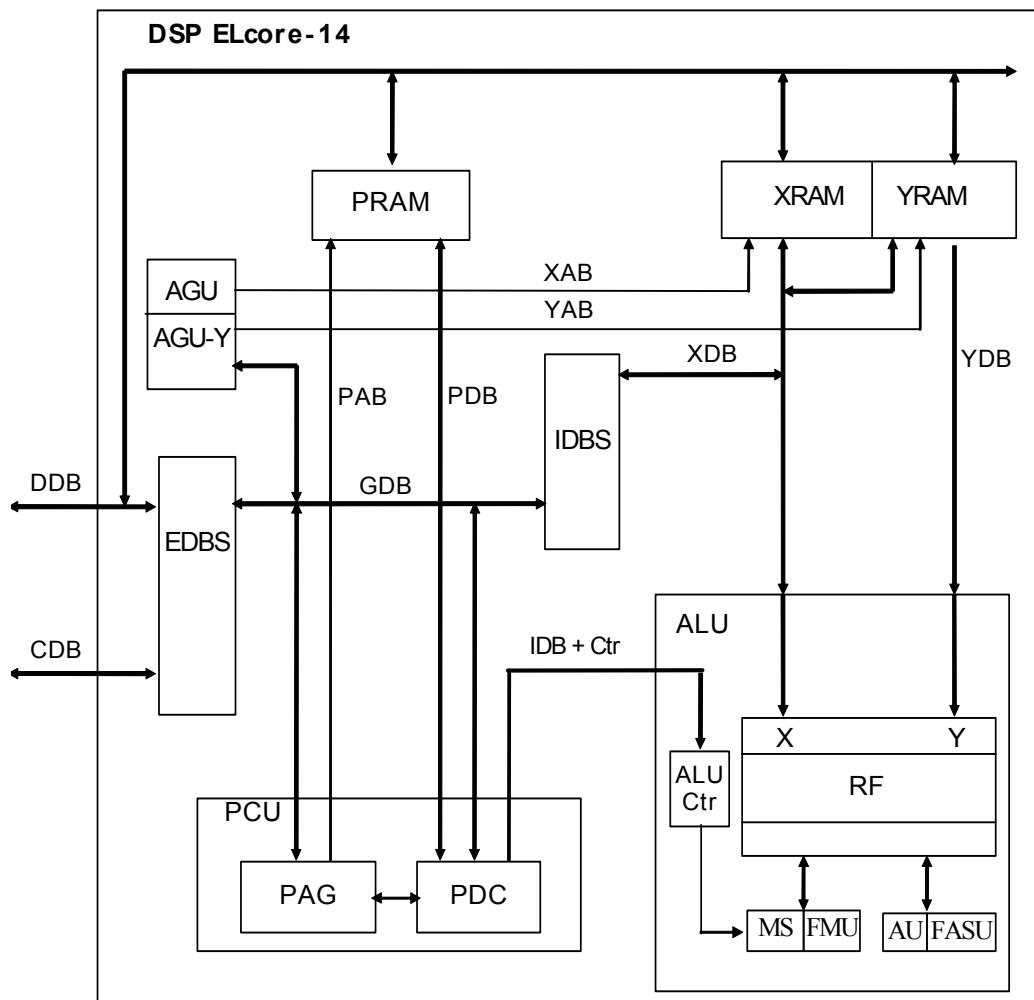

| 3.2.1    | <i>Структурная схема DSP</i> .....                                                                                                   | 82 |

|          |                                                                     |     |

|----------|---------------------------------------------------------------------|-----|

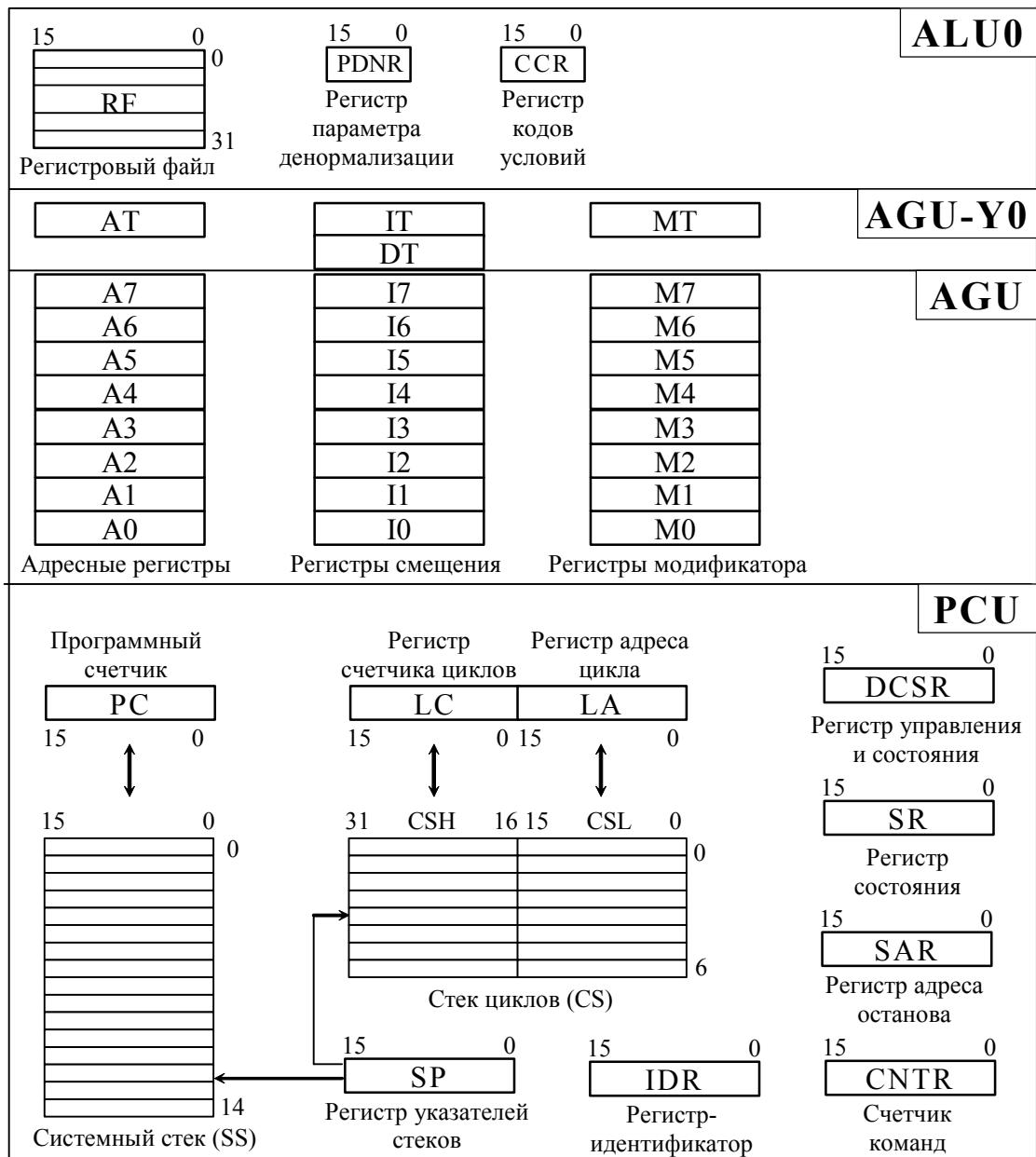

| 3.2.2    | <i>Арифметико-логическое устройство (ALU)</i> .....                 | 83  |

| 3.2.3    | <i>Устройства генерации адреса (AGU, AGU-Y)</i> .....               | 85  |

| 3.2.4    | <i>Устройство программного управления (PCU)</i> .....               | 85  |

| 3.2.5    | <i>Коммутаторы шин данных (IDBS, EDBS)</i> .....                    | 85  |

| 3.2.6    | <i>Блоки памяти</i> .....                                           | 85  |

| 3.2.7    | <i>Шины адреса и данных</i> .....                                   | 86  |

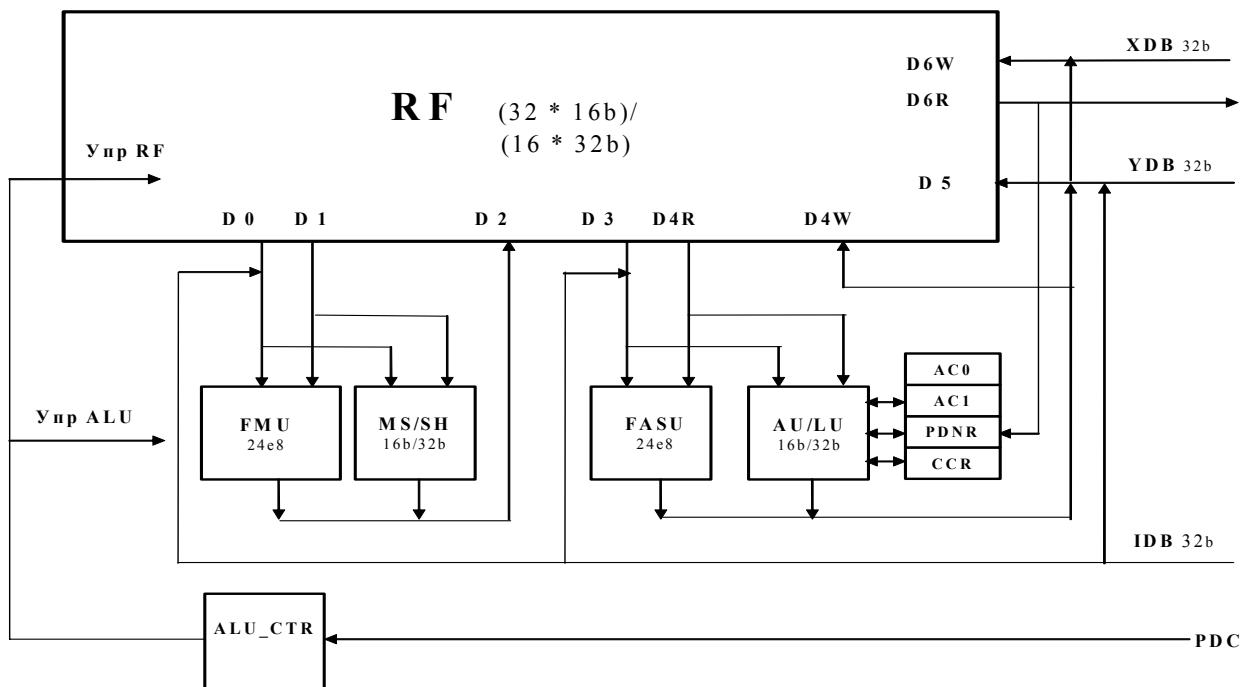

| 3.3      | <b>АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО (ALU)</b> .....                 | 87  |

| 3.3.1    | <i>Архитектура ALU</i> .....                                        | 87  |

| 3.3.1.1  | Регистровый файл .....                                              | 89  |

| 3.3.1.2  | Операционные устройства .....                                       | 90  |

| 3.3.1.3  | Регистр PDNR .....                                                  | 91  |

| 3.3.1.4  | Регистр CCR .....                                                   | 91  |

| 3.3.1.5  | Регистры-аккумуляторы AC0, AC1 .....                                | 94  |

| 3.3.2    | <i>Режимы работы ALU</i> .....                                      | 94  |

| 3.3.2.1  | Округление (Rounding) .....                                         | 94  |

| 3.3.2.2  | Масштабирование (Scaling) .....                                     | 95  |

| 3.3.2.3  | Поддержка режима блочной экспоненты .....                           | 96  |

| 3.3.2.4  | Режим насыщения (Saturation) .....                                  | 97  |

| 3.4      | <b>УСТРОЙСТВА ГЕНЕРАЦИИ АДРЕСОВ ПАМЯТИ ДАННЫХ (AGU,AGU-Y)</b> ..... | 98  |

| 3.4.1    | <i>Архитектура AGU</i> .....                                        | 98  |

| 3.4.2    | <i>Программная модель AGU</i> .....                                 | 100 |

| 3.4.2.1  | Адресный регистровый файл .....                                     | 100 |

| 3.4.2.2  | Регистровый файл смещений .....                                     | 100 |

| 3.4.2.3  | Регистровый файл модификаторов .....                                | 100 |

| 3.4.3    | <i>Архитектура AGU-Y</i> .....                                      | 101 |

| 3.4.4    | <i>Программная модель AGU-Y</i> .....                               | 102 |

| 3.4.5    | <i>Виды адресации</i> .....                                         | 102 |

| 3.4.5.1  | Прямая регистровая адресация .....                                  | 103 |

| 3.4.5.2  | Виды адресации программной памяти .....                             | 104 |

| 3.4.5.3  | Косвенная адресация памяти данных .....                             | 104 |

| 3.4.6    | <i>Типы адресной арифметики</i> .....                               | 106 |

| 3.4.7    | <i>Режимы адресации</i> .....                                       | 108 |

| 3.4.7.1  | Режимы адресации AGU .....                                          | 108 |

| 3.4.7.2  | Режимы адресации AGU-Y .....                                        | 109 |

| 3.5      | <b>УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ (PCU)</b> .....               | 109 |

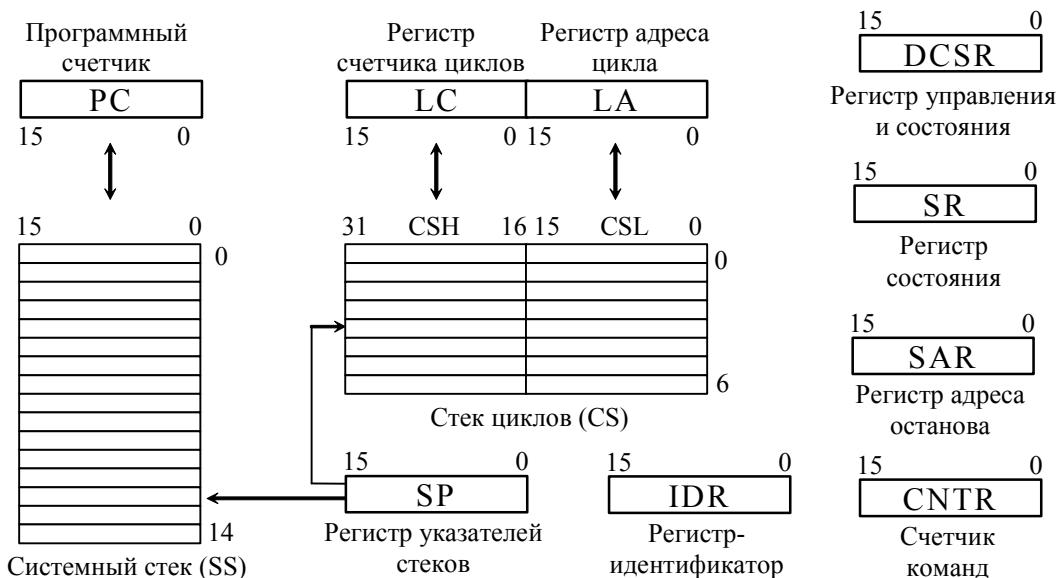

| 3.5.1    | <i>Назначение и состав PCU</i> .....                                | 109 |

| 3.5.2    | <i>Архитектура PCU</i> .....                                        | 110 |

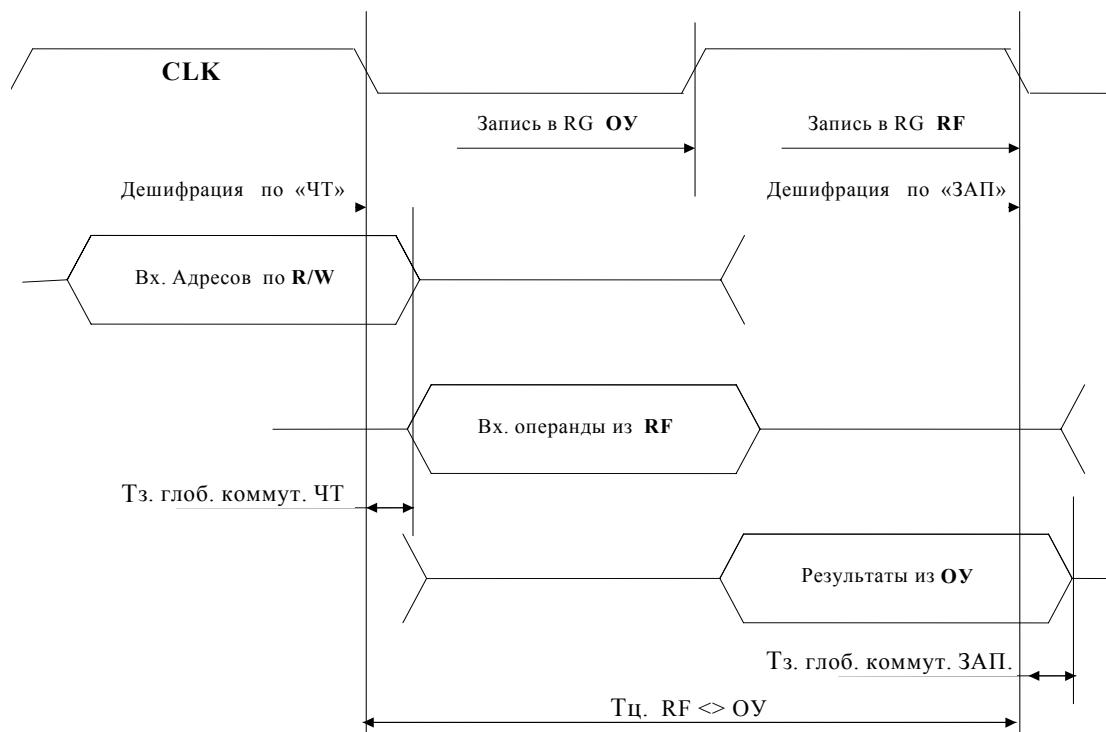

| 3.5.3    | <i>Программный конвейер</i> .....                                   | 111 |

| 3.5.4    | <i>Программная модель PCU</i> .....                                 | 112 |

| 3.5.4.1  | Регистр-идентификатор (IDR) .....                                   | 112 |

| 3.5.4.2  | Регистр управления и состояния (DCSR) .....                         | 113 |

| 3.5.4.3  | Регистр программного счетчика (PC) .....                            | 114 |

| 3.5.4.4  | Регистр состояния (SR) .....                                        | 115 |

| 3.5.4.5  | Регистр счетчика циклов (LC) .....                                  | 115 |

| 3.5.4.6  | Регистр адреса цикла (LA) .....                                     | 116 |

| 3.5.4.7  | Системный стек (SS) .....                                           | 116 |

| 3.5.4.8  | Стек цикла (CS) .....                                               | 117 |

| 3.5.4.9  | Регистр указателей стека (SP) .....                                 | 117 |

| 3.5.4.10 | Счетчик команд (CNTR) .....                                         | 120 |

| 3.6      | <b>ПРОГРАММНАЯ МОДЕЛЬ DSP</b> .....                                 | 121 |

| 3.7      | <b>Состояния DSP</b> .....                                          | 122 |

| 3.7.1    | <i>Состояние начальной установки (RESET)</i> .....                  | 122 |

| 3.7.2    | <i>Состояние останова (STOP)</i> .....                              | 122 |

| 3.7.3    | <i>Состояние исполнения программы (RUN)</i> .....                   | 123 |

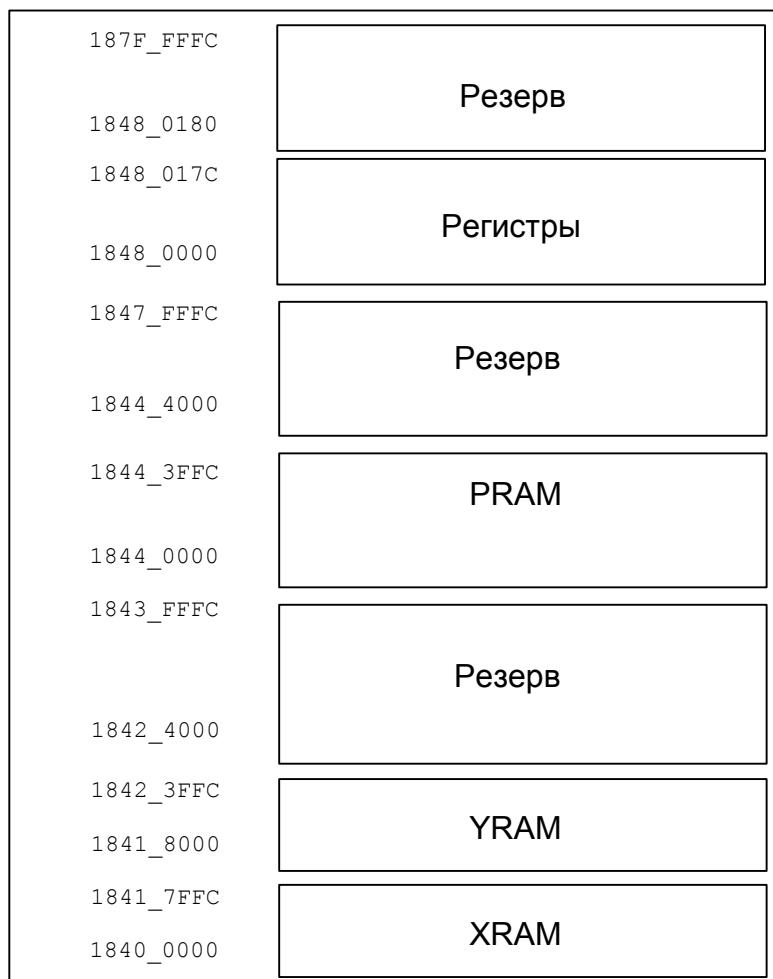

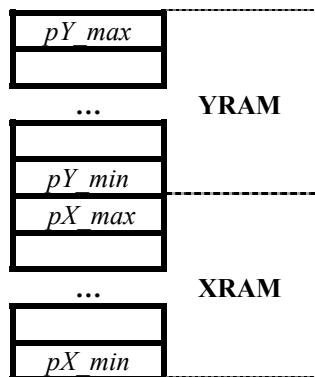

| 3.8      | <b>КАРТА ПАМЯТИ DSP</b> .....                                       | 124 |

| 3.8.1    | <i>Организация обменов с памятью данных</i> .....                   | 125 |

| 3.8.2    | <i>Организация памяти программ PRAM</i> .....                       | 126 |

| 3.8.3    | <i>Адресуемые регистры</i> .....                                    | 126 |

|       |                                                                |     |

|-------|----------------------------------------------------------------|-----|

| 4.    | СИСТЕМНОЕ УПРАВЛЕНИЕ .....                                     | 129 |

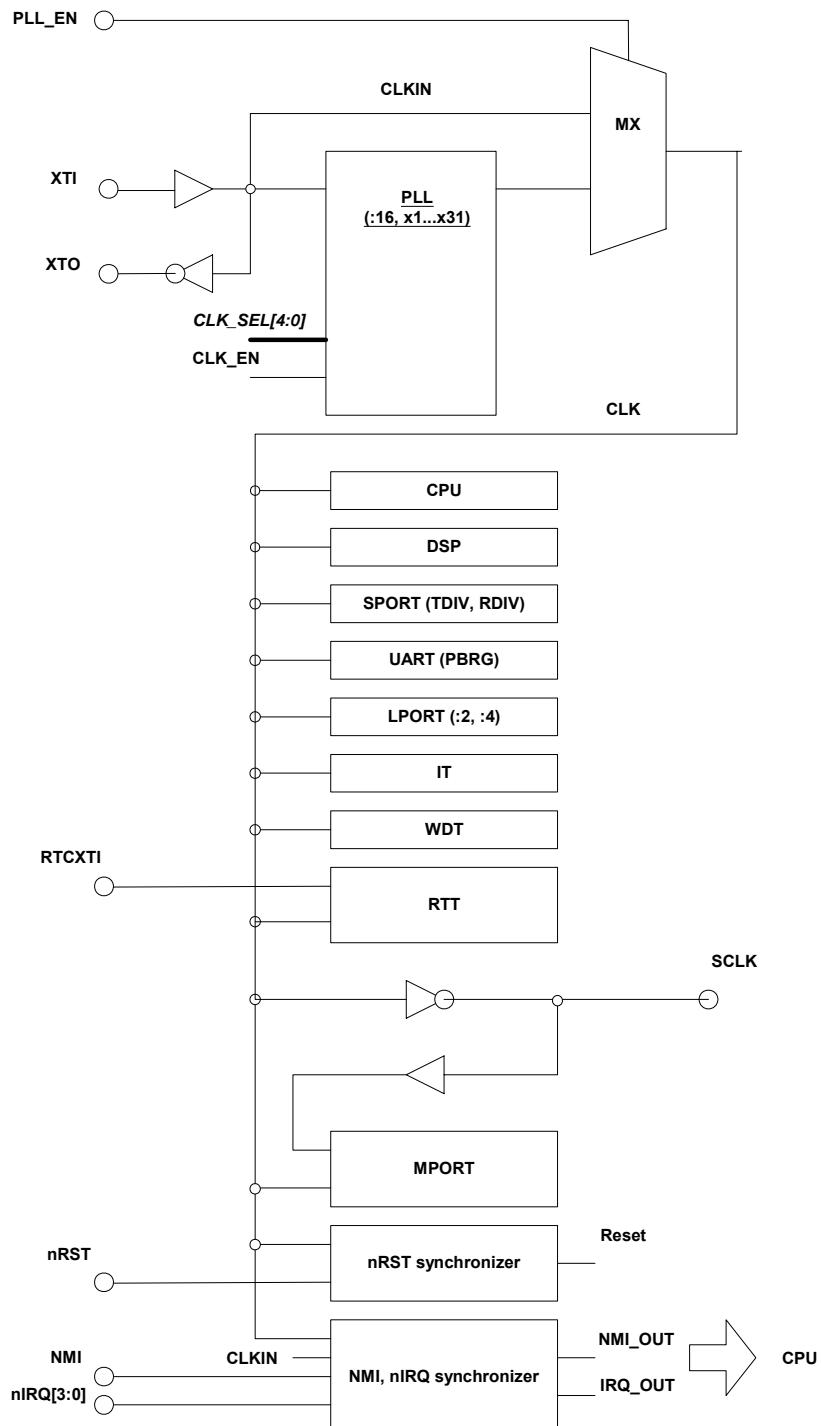

| 4.1   | СИСТЕМА СИНХРОНИЗАЦИИ .....                                    | 129 |

| 4.2   | ОТКЛЮЧЕНИЕ И ВКЛЮЧЕНИЕ ТАКТОВОЙ ЧАСТОТЫ .....                  | 131 |

| 4.3   | СИСТЕМНЫЕ РЕГИСТРЫ.....                                        | 132 |

| 4.3.1 | <i>Регистр управления и состояния CSR</i> .....                | 132 |

| 4.3.2 | <i>Регистр запросов прерывания QSTR</i> .....                  | 132 |

| 4.3.3 | <i>Регистр маски MASKR</i> .....                               | 134 |

| 4.4   | ПРОЦЕДУРА НАЧАЛЬНОЙ ЗАГРУЗКИ.....                              | 134 |

| 4.5   | ЛОГИКА ВЗАИМОДЕЙСТВИЯ CPU И DSP .....                          | 134 |

| 4.5.1 | <i>Функции CPU</i> .....                                       | 134 |

| 4.5.2 | <i>Функции DSP</i> .....                                       | 135 |

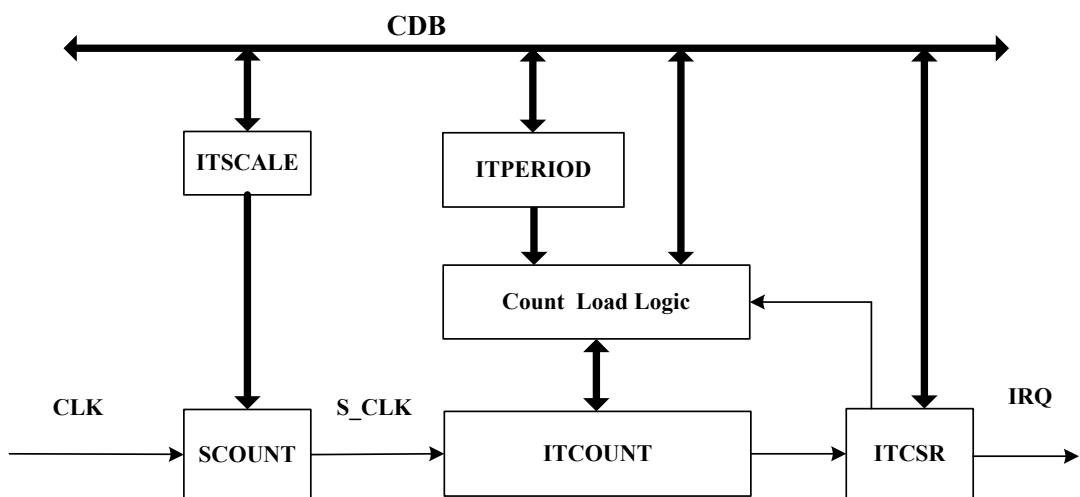

| 5.    | ИНТЕРВАЛЬНЫЙ ТАЙМЕР .....                                      | 136 |

| 5.1   | НАЗНАЧЕНИЕ.....                                                | 136 |

| 5.2   | СТРУКТУРНАЯ СХЕМА .....                                        | 136 |

| 5.3   | РЕГИСТРЫ ИНТЕРВАЛЬНОГО ТАЙМЕРА .....                           | 137 |

| 5.4   | ПРОГРАММИРОВАНИЕ ИТ .....                                      | 138 |

| 6.    | ТАЙМЕР РЕАЛЬНОГО ВРЕМЕНИ .....                                 | 139 |

| 6.1   | НАЗНАЧЕНИЕ.....                                                | 139 |

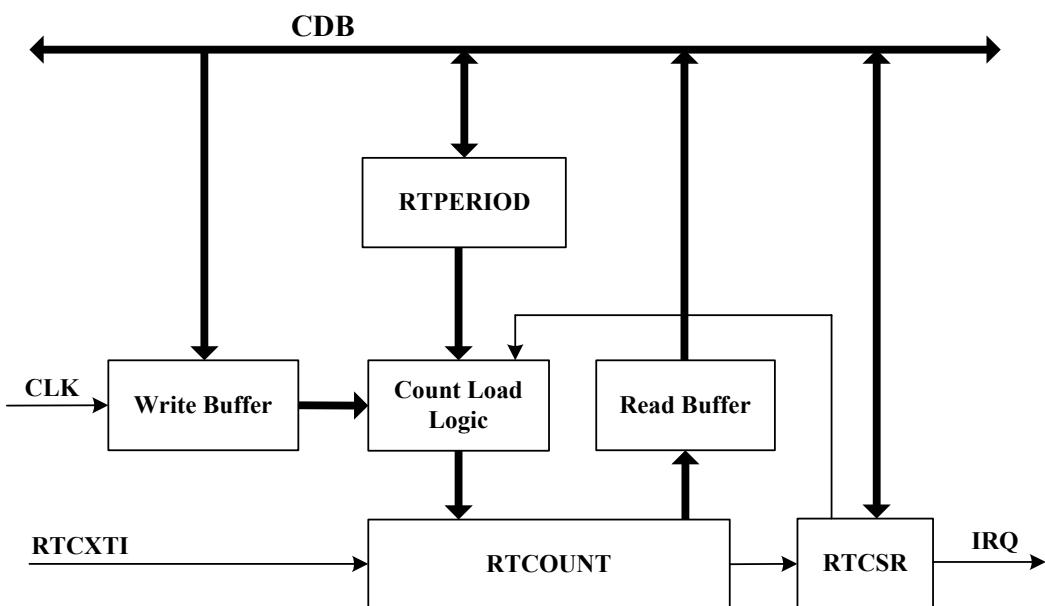

| 6.2   | СТРУКТУРНАЯ СХЕМА RTT .....                                    | 139 |

| 6.3   | ОПИСАНИЕ РЕГИСТРОВ ТАЙМЕРА РЕАЛЬНОГО ВРЕМЕНИ.....              | 140 |

| 6.4   | ПРОГРАММИРОВАНИЕ RTT .....                                     | 141 |

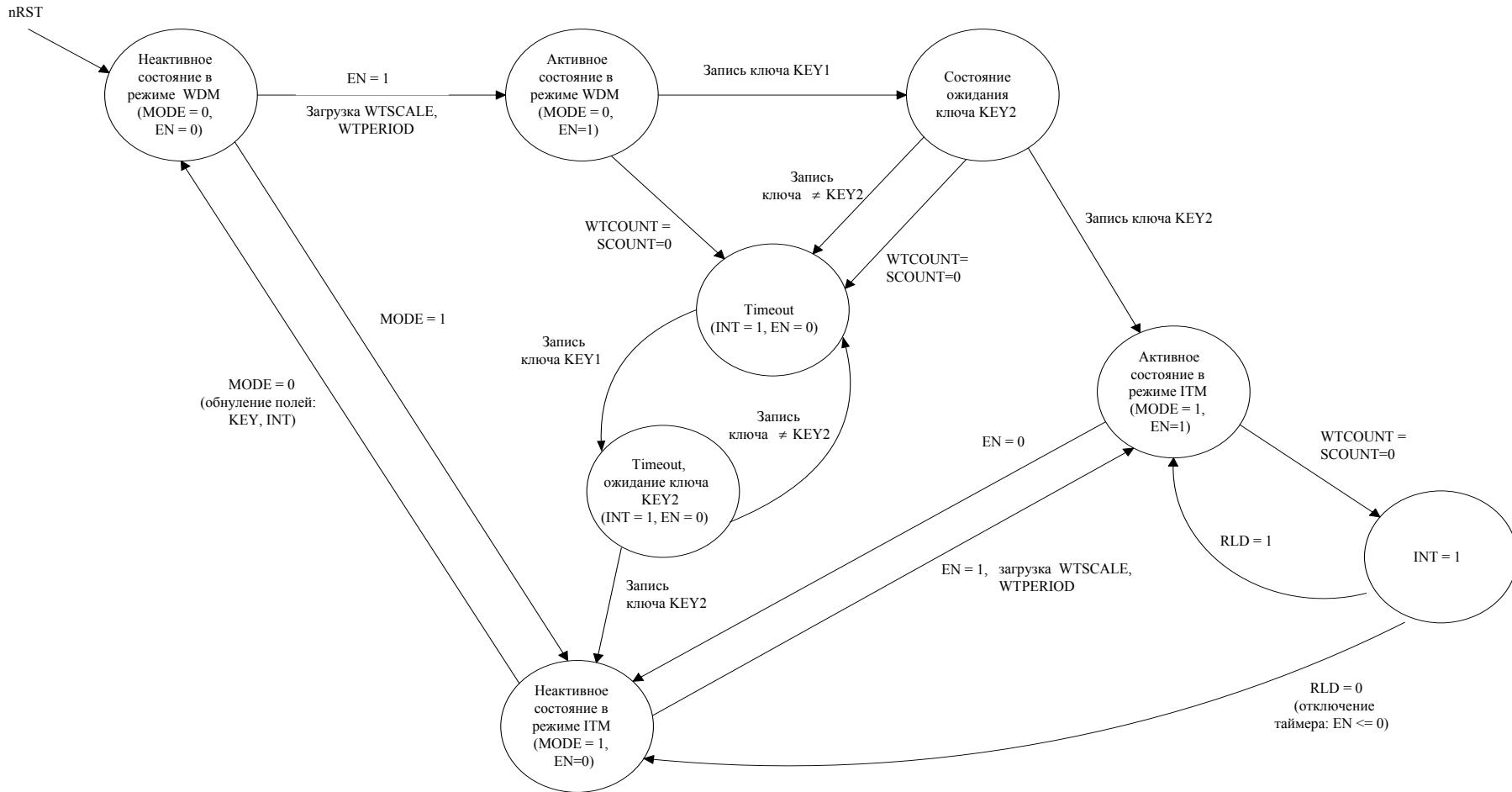

| 7.    | СТОРОЖЕВОЙ ТАЙМЕР .....                                        | 142 |

| 7.1   | НАЗНАЧЕНИЕ.....                                                | 142 |

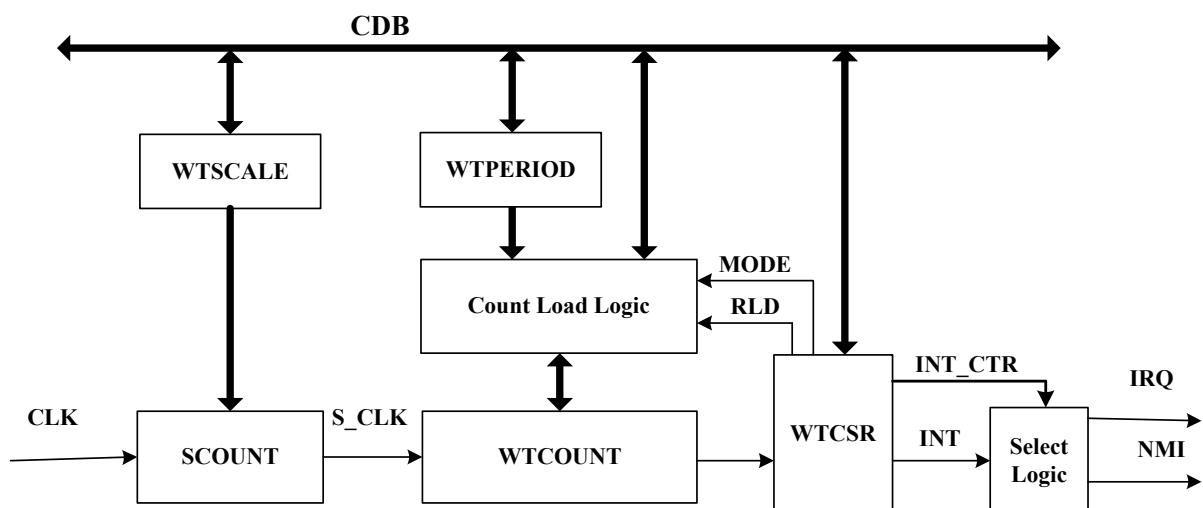

| 7.2   | СТРУКТУРНАЯ СХЕМА .....                                        | 142 |

| 7.3   | ОПИСАНИЕ РЕГИСТРОВ WDT .....                                   | 143 |

| 7.4   | ПРОГРАММИРОВАНИЕ WDT .....                                     | 145 |

| 8.    | КОНТРОЛЛЕР ПРЯМОГО ДОСТУПА В ПАМЯТЬ (DMA) .....                | 148 |

| 8.1   | Общие положения .....                                          | 148 |

| 8.1.1 | <i>Типы каналов</i> .....                                      | 148 |

| 8.1.2 | <i>Приоритет каналов DMA и CPU</i> .....                       | 148 |

| 8.1.3 | <i>Темп передачи</i> .....                                     | 149 |

| 8.1.4 | <i>Регистры DMA</i> .....                                      | 150 |

| 8.1.5 | <i>Прерывания DMA</i> .....                                    | 150 |

| 8.2   | ПРОЦЕДУРА САМОИНИЦИАЛИЗАЦИИ.....                               | 150 |

| 8.3   | КАНАЛЫ DMA ПОСЛЕДОВАТЕЛЬНЫХ ПОРТОВ .....                       | 151 |

| 8.4   | КАНАЛЫ DMA ЛИНКОВЫХ ПОРТОВ .....                               | 155 |

| 8.5   | КАНАЛЫ ОБМЕНА ДАННЫМИ МЕЖДУ ВНУТРЕННЕЙ И ВНЕШНЕЙ ПАМЯТЬЮ ..... | 156 |

| 9.    | ПОРТ ВНЕШНЕЙ ПАМЯТИ .....                                      | 159 |

| 9.1   | ВВЕДЕНИЕ .....                                                 | 159 |

| 9.2   | РЕГИСТРЫ ПОРТА ВНЕШНЕЙ ПАМЯТИ .....                            | 159 |

| 9.2.1 | <i>Регистр конфигурации CSCON0</i> .....                       | 160 |

| 9.2.2 | <i>Регистр конфигурации CSCON1</i> .....                       | 161 |

| 9.2.3 | <i>Регистр конфигурации CSCON2</i> .....                       | 161 |

| 9.2.4 | <i>Регистр конфигурации CSCON3</i> .....                       | 162 |

| 9.2.5 | <i>Регистр конфигурации CSCON4</i> .....                       | 163 |

| 9.2.6 | <i>Регистр управления работой с памятью SDRAM</i> .....        | 163 |

| 9.2.7 | <i>Регистр CKE_CTR</i> .....                                   | 164 |

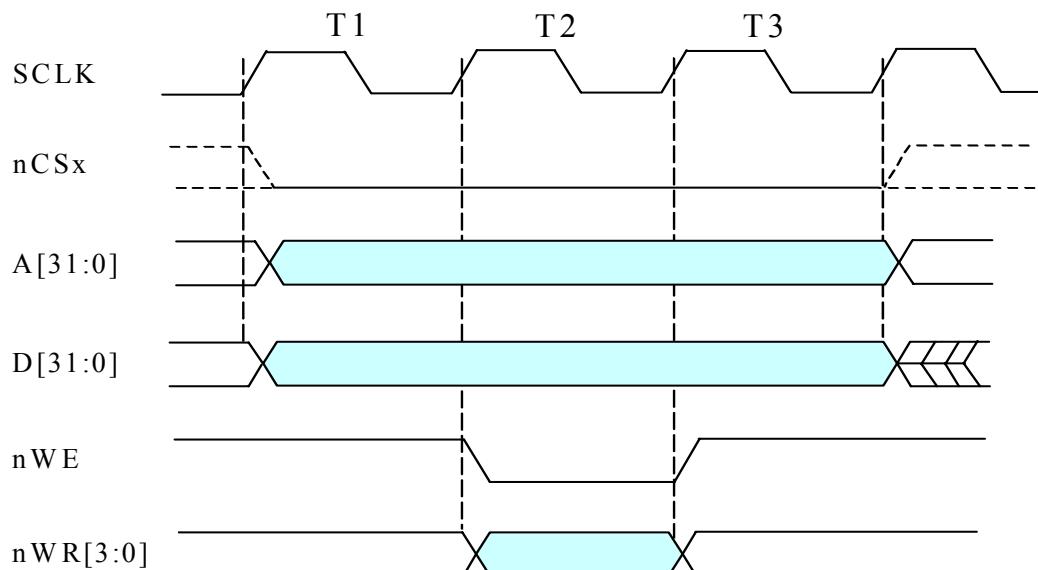

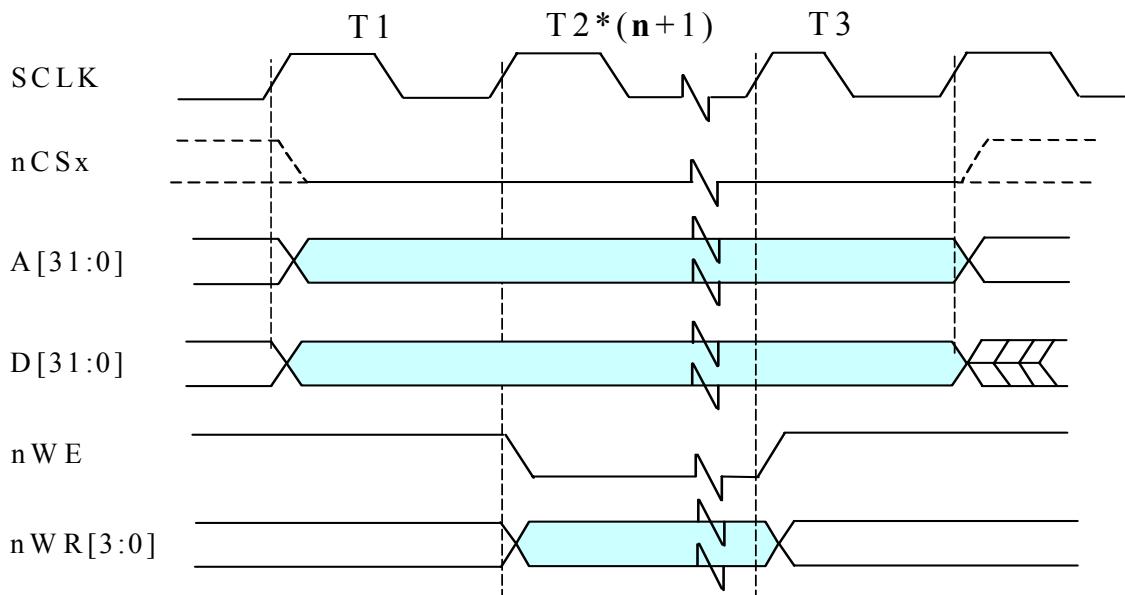

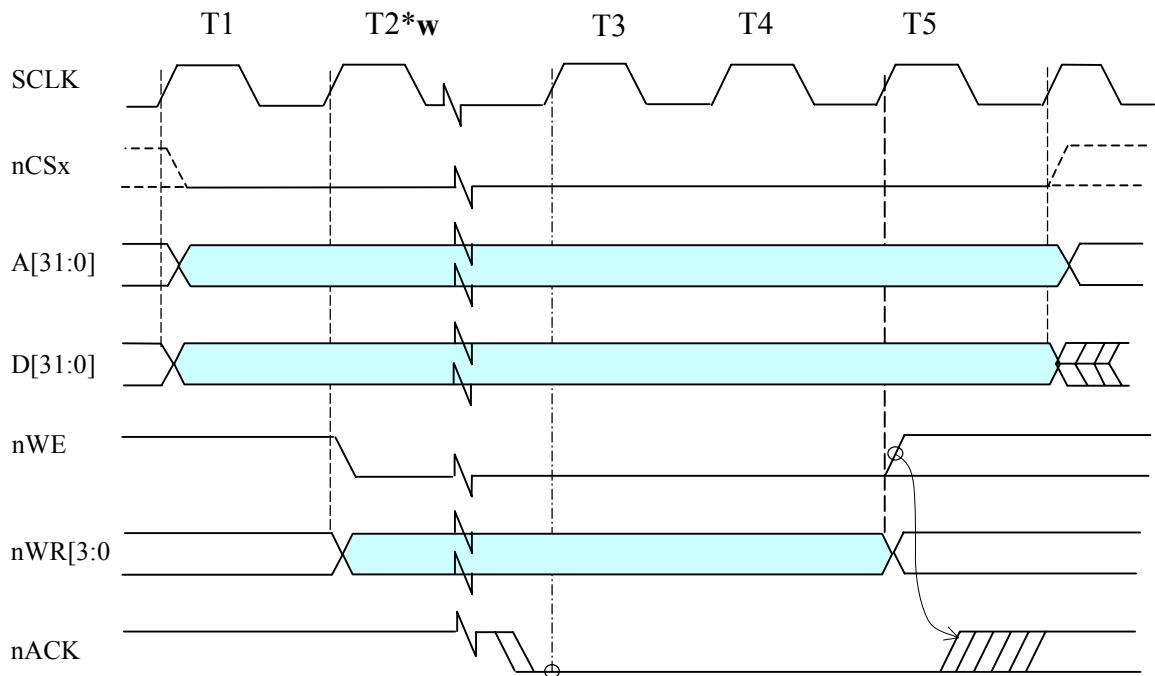

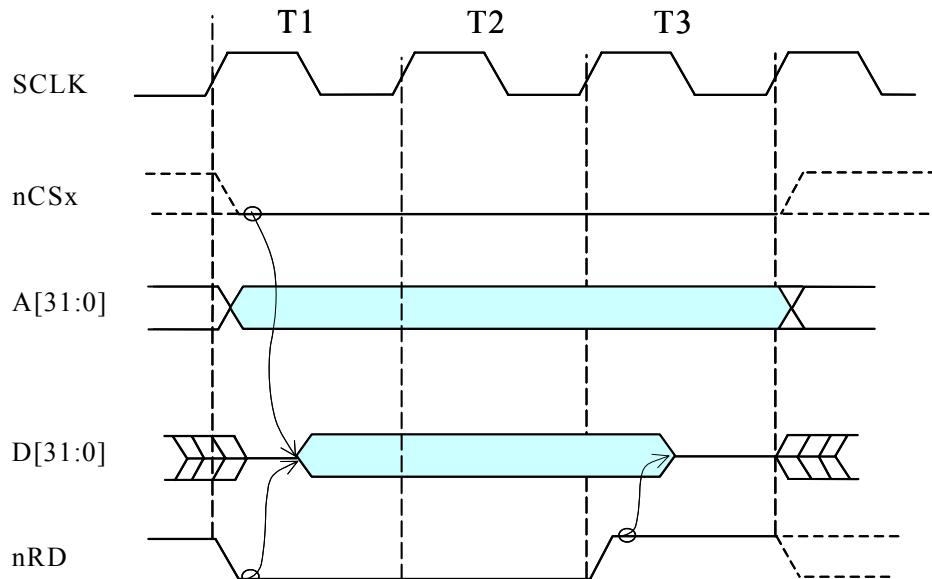

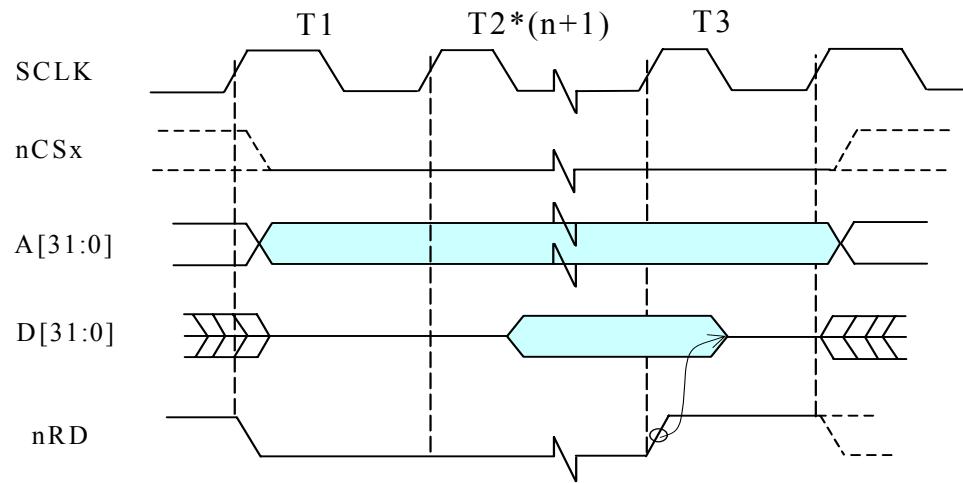

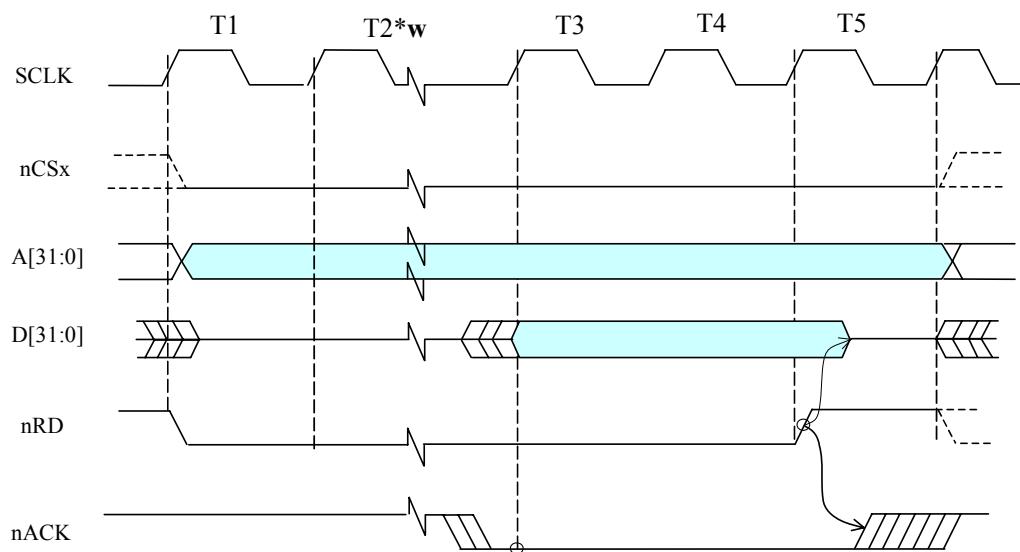

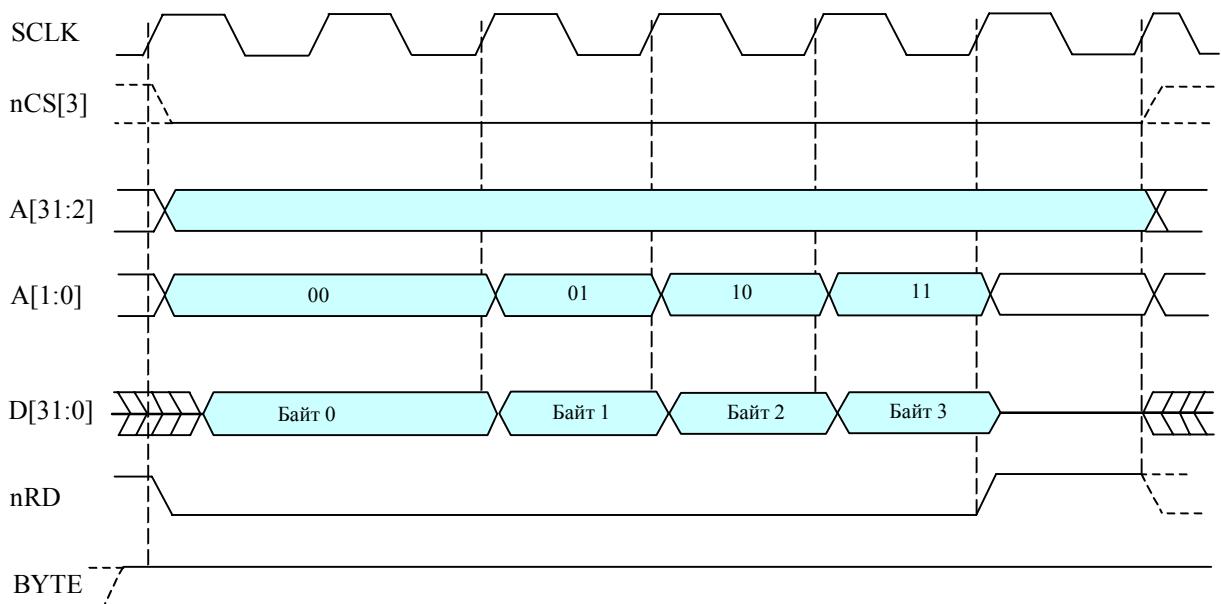

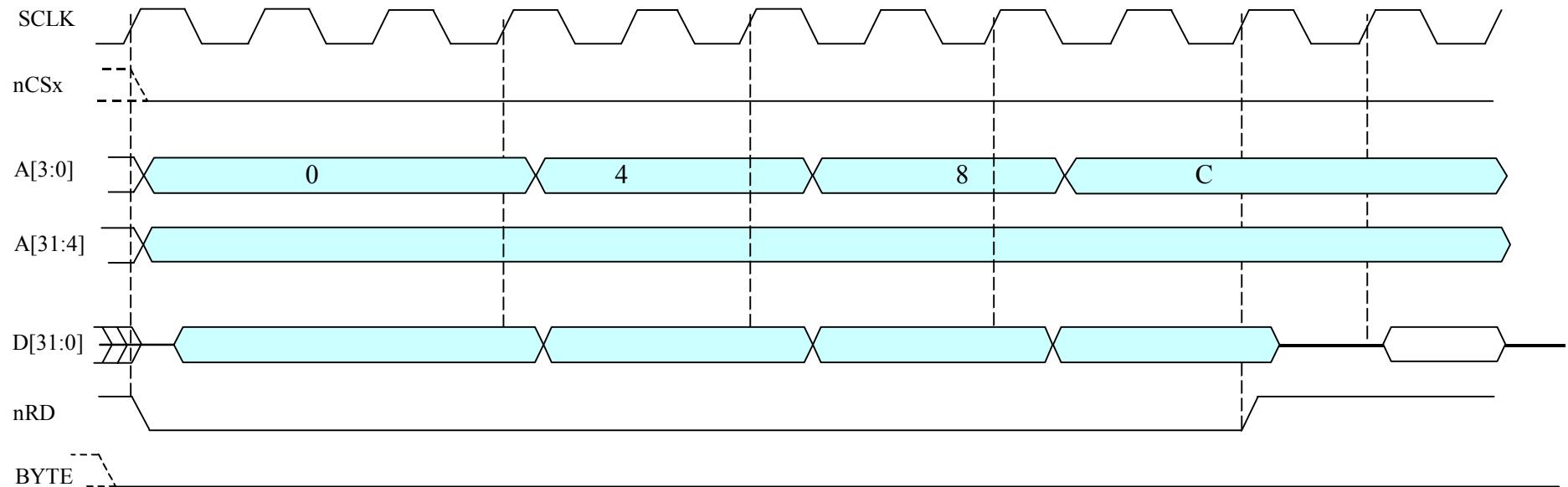

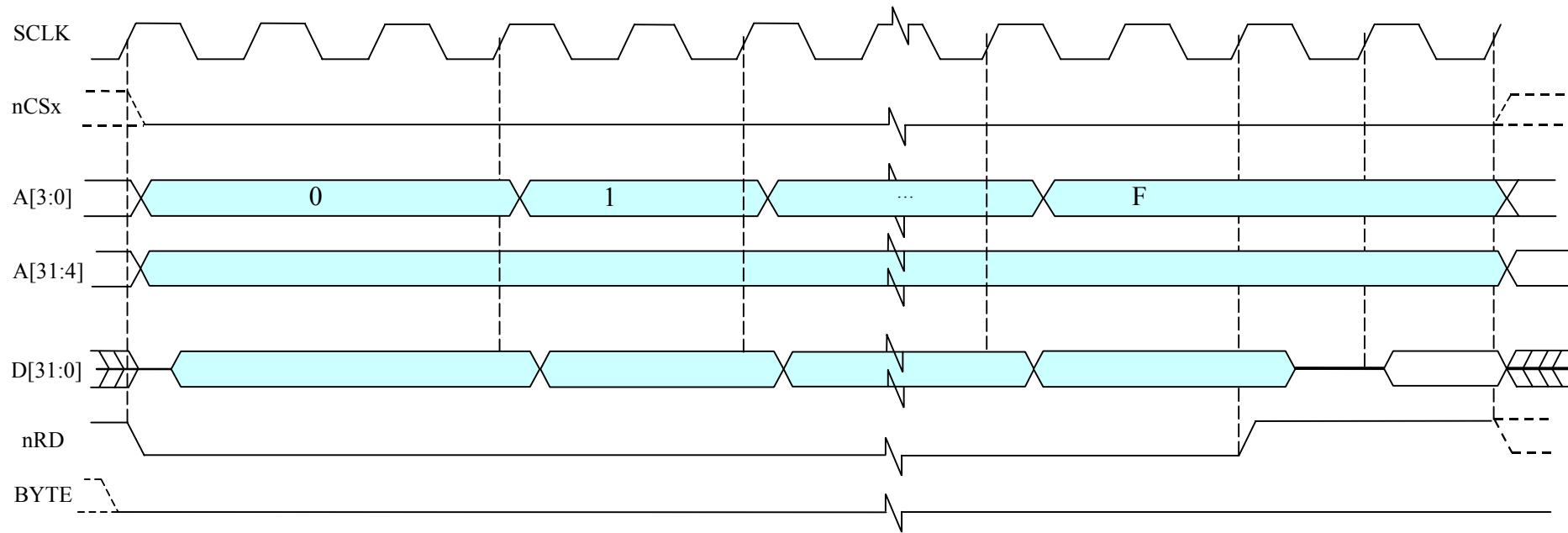

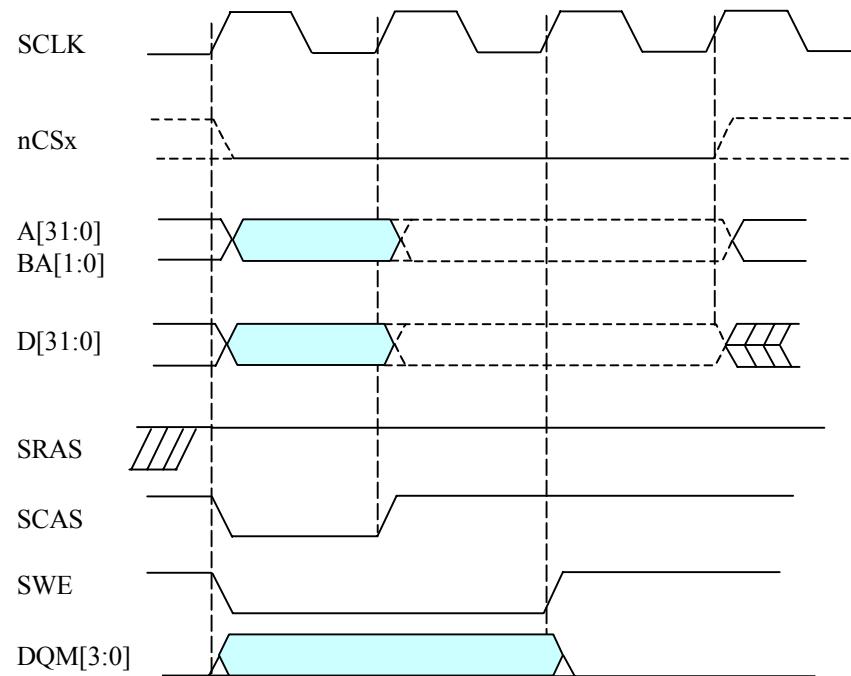

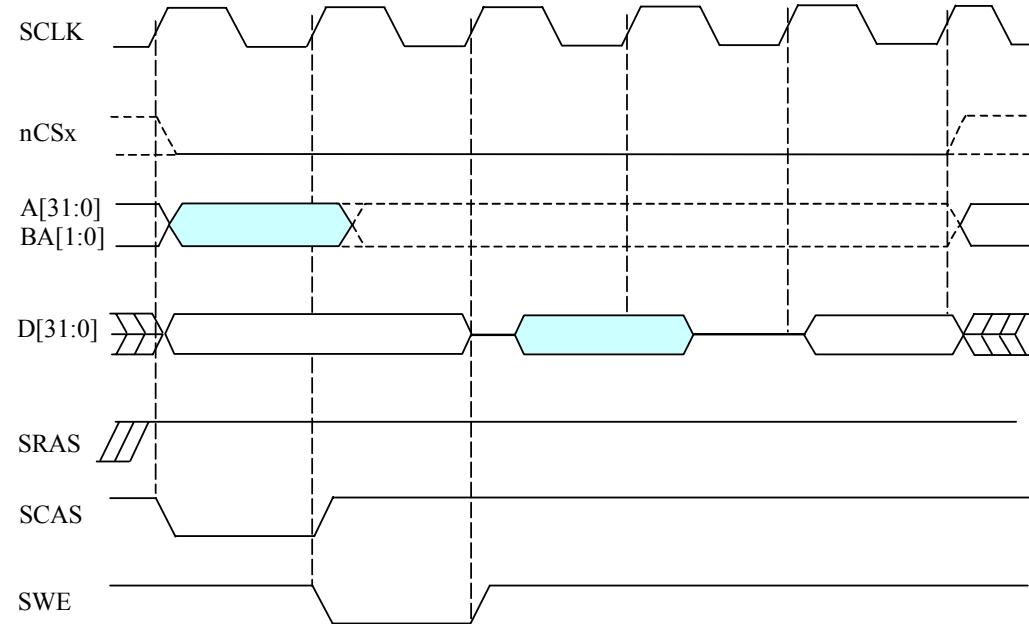

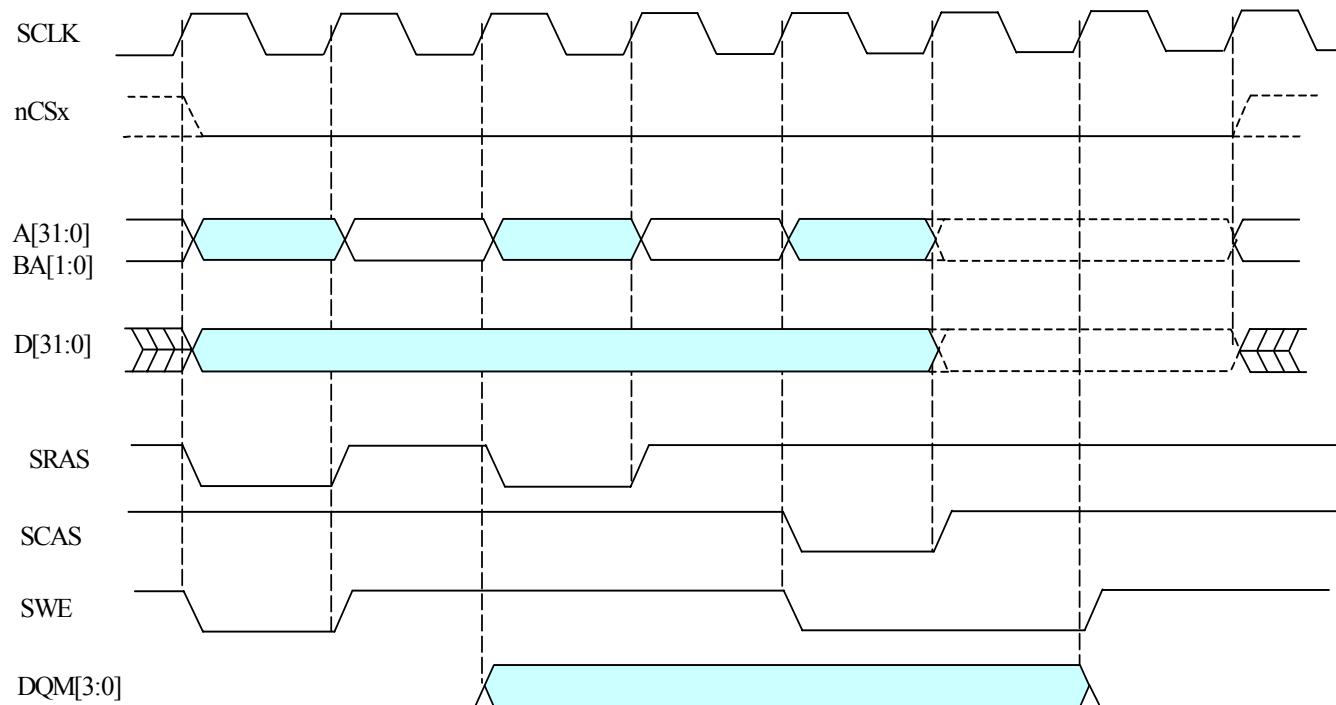

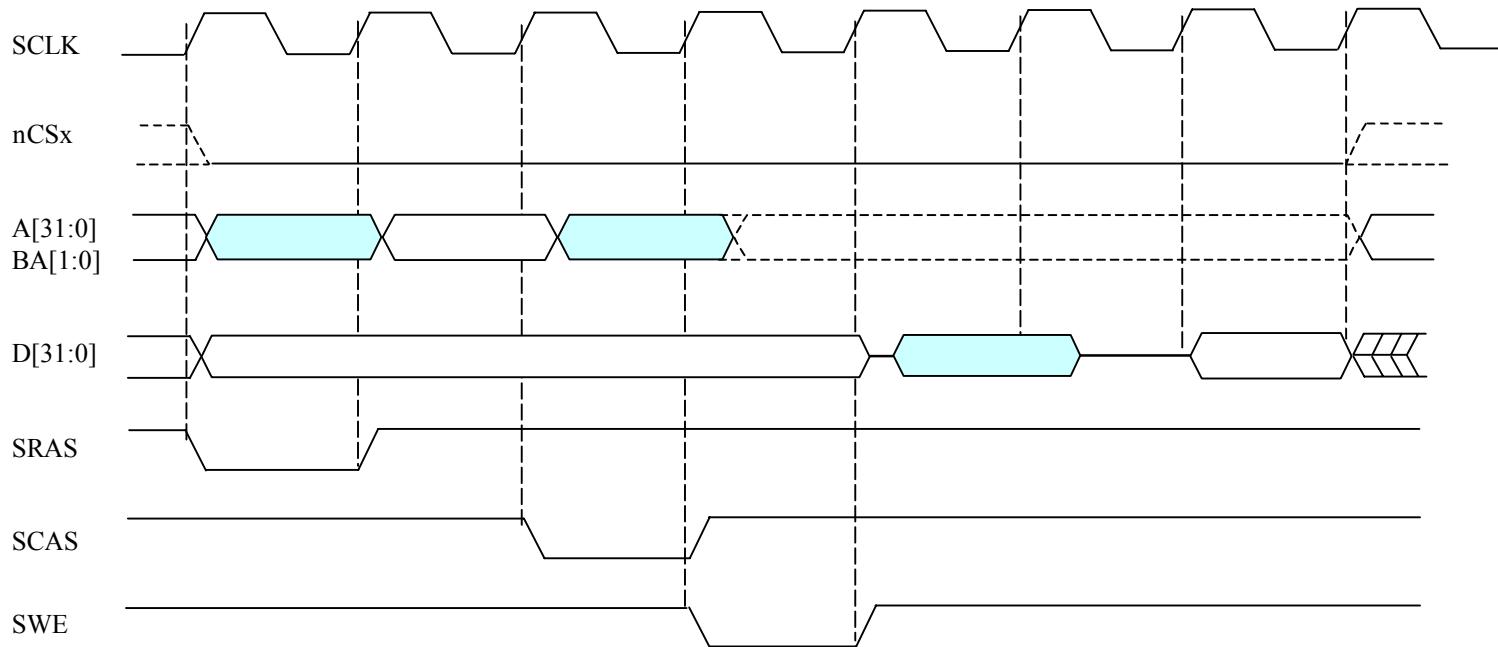

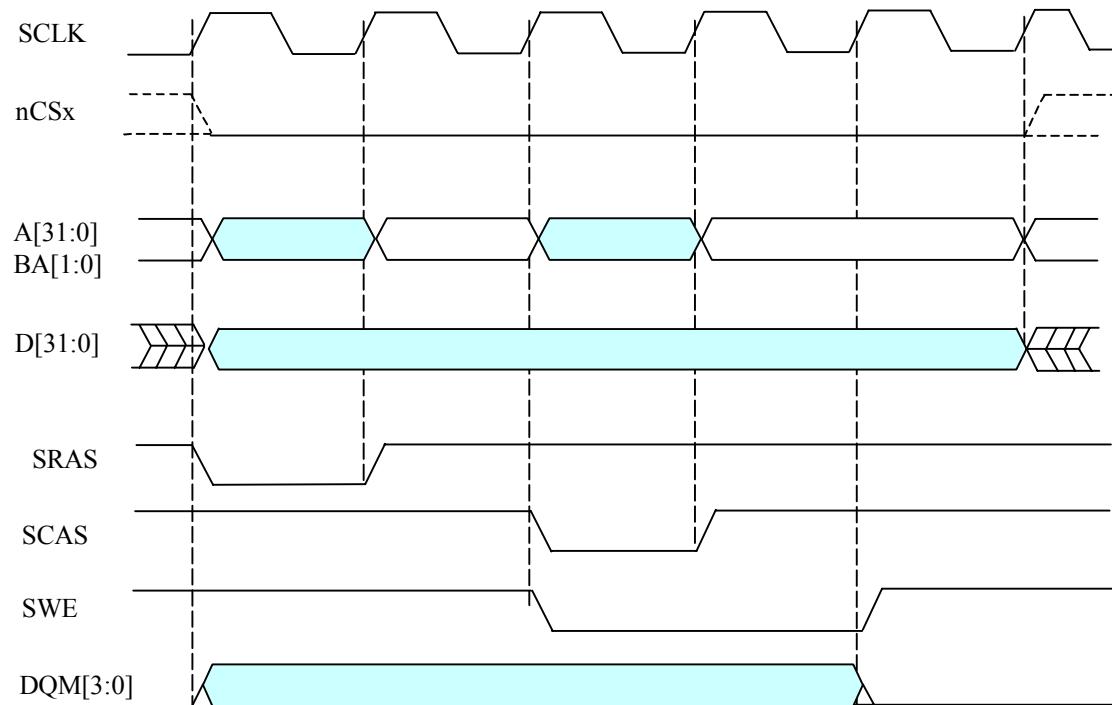

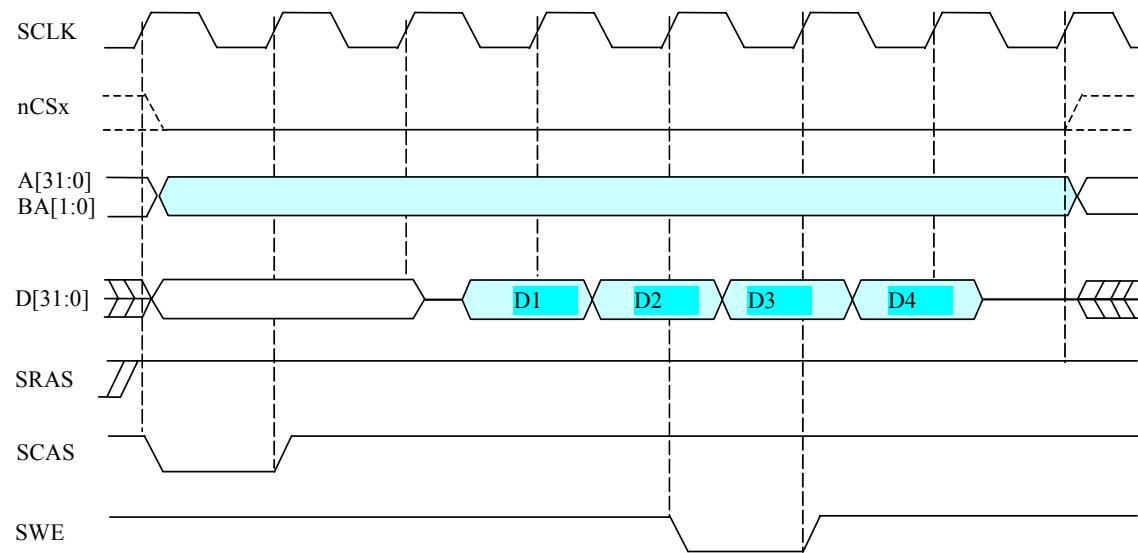

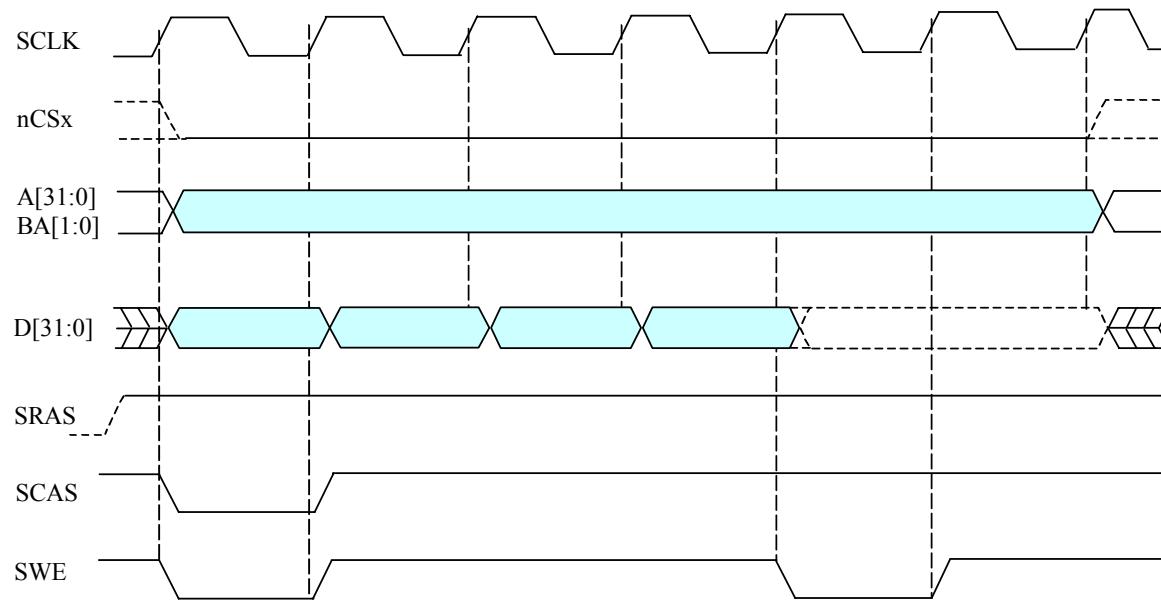

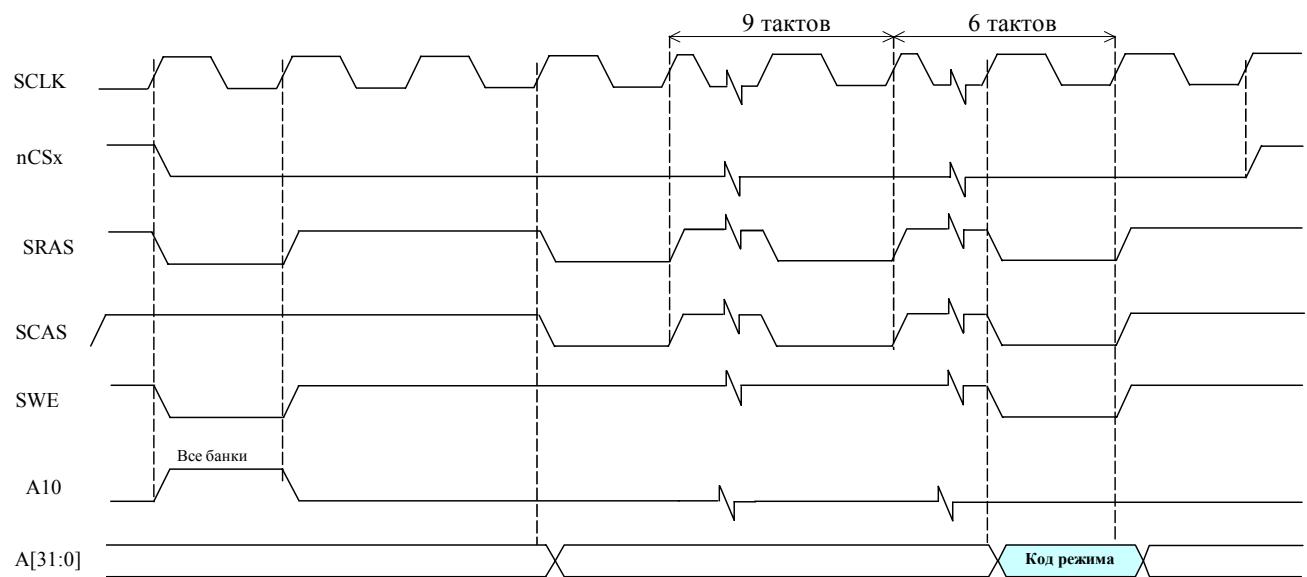

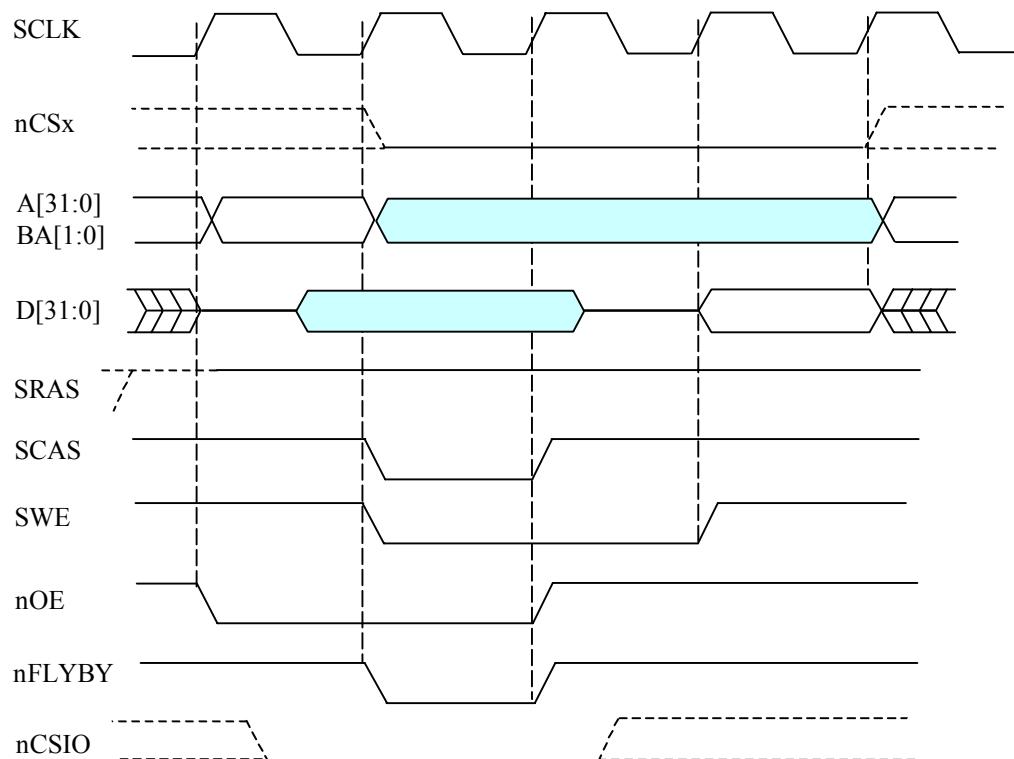

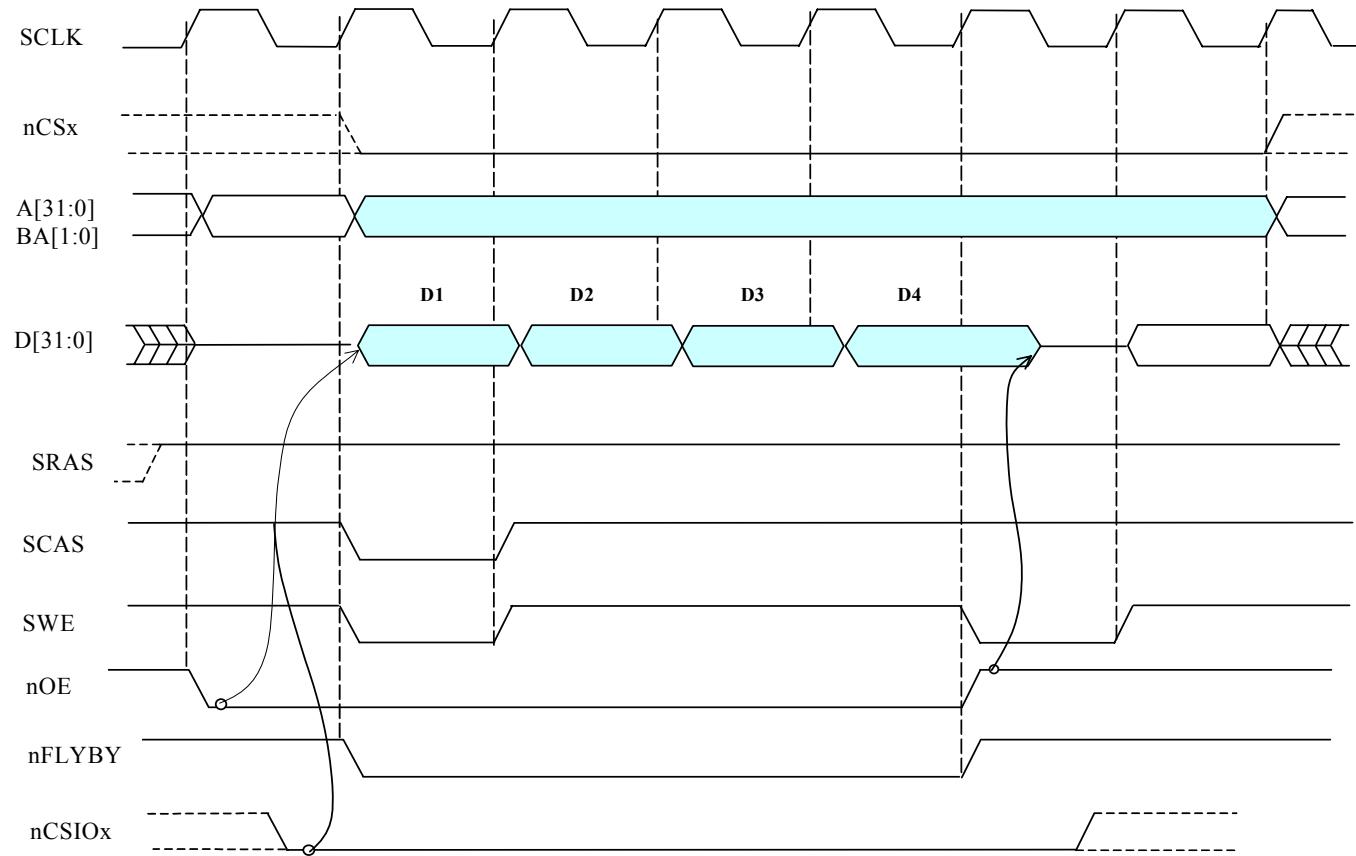

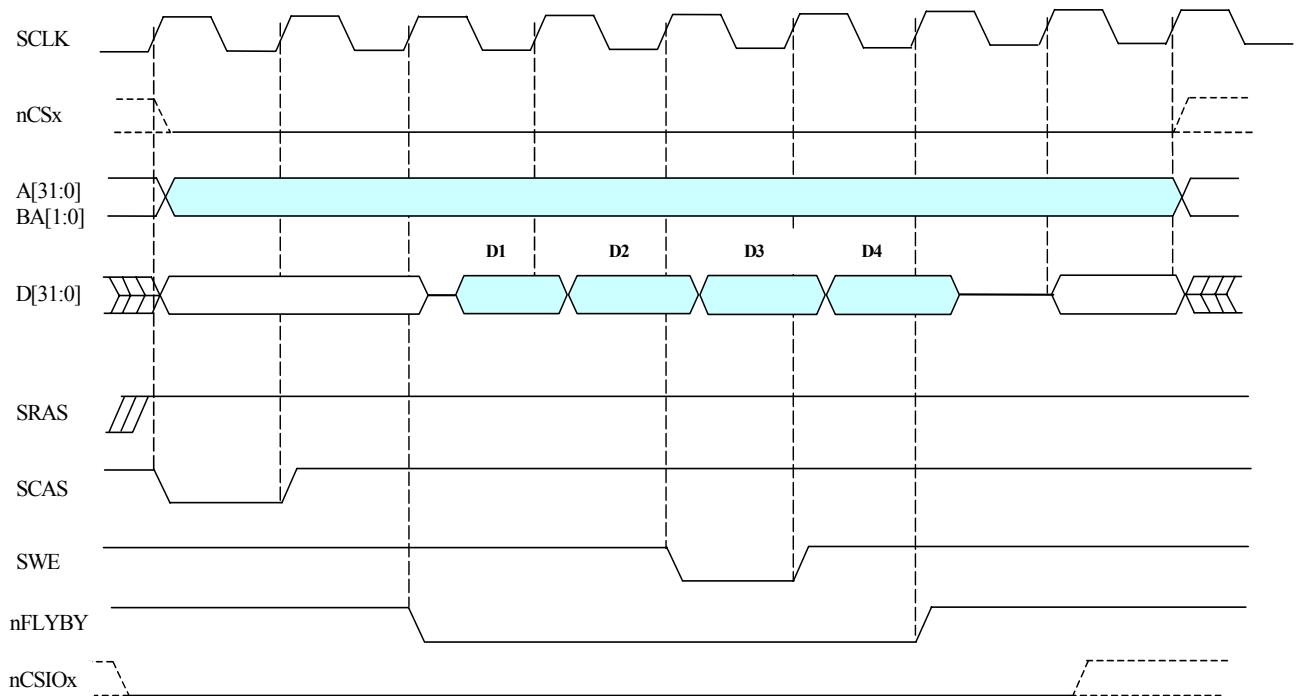

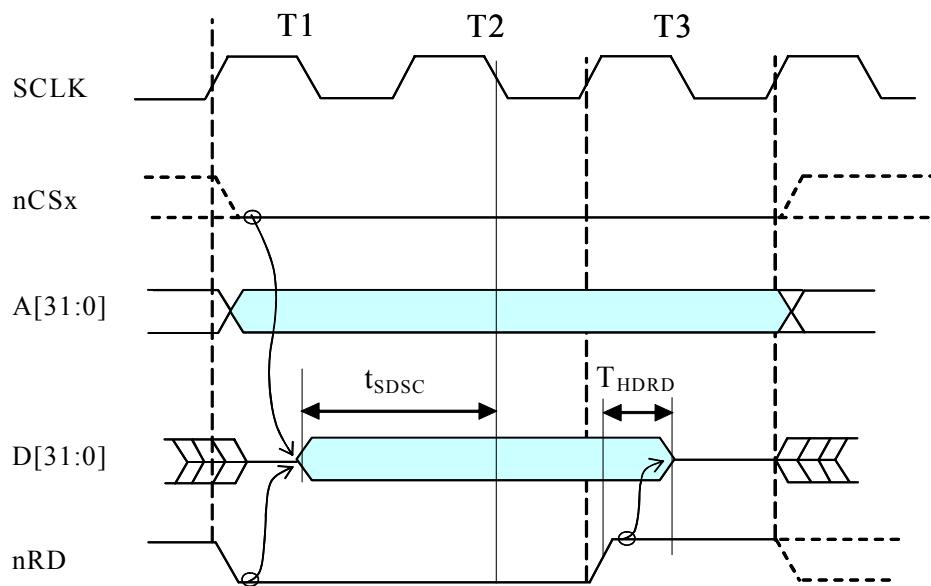

| 9.3   | ВРЕМЕННЫЕ ДИАГРАММЫ ОБМЕНА ДАННЫМИ .....                       | 165 |

| 9.3.1 | <i>Общие положения</i> .....                                   | 165 |

| 9.3.2 | <i>Обмен данными с асинхронной памятью</i> .....               | 166 |

| 9.3.3 | <i>Обмен данными с синхронной памятью</i> .....                | 174 |

| 9.3.4 | <i>Обмен данными в режиме Flyby</i> .....                      | 182 |

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| 9.4 РЕКОМЕНДАЦИИ ПО ПОДКЛЮЧЕНИЮ ВНЕШНЕЙ ПАМЯТИ.....                               | 187 |

| 9.4.1 <i>Память тайна SDRAM</i> .....                                             | 187 |

| 9.4.2 <i>Память тайна Flash</i> .....                                             | 187 |

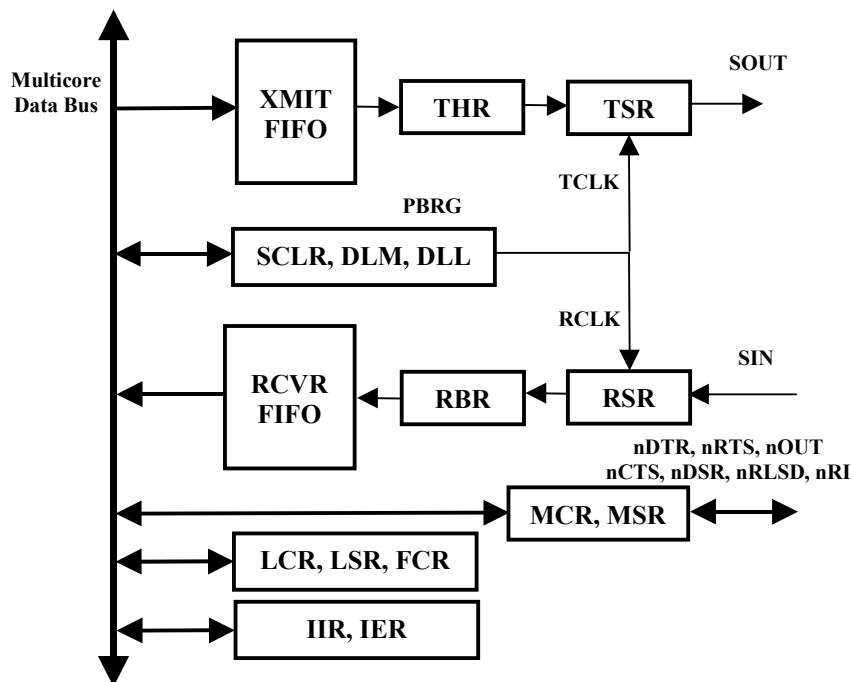

| 10. УНИВЕРСАЛЬНЫЙ АСИНХРОННЫЙ ПОРТ (UART).....                                    | 188 |

| 10.1 Общие положения .....                                                        | 188 |

| 10.2 Регистры UART .....                                                          | 189 |

| 10.2.1 <i>Общие положения</i> .....                                               | 189 |

| 10.2.2 <i>Регистр LCR</i> .....                                                   | 190 |

| 10.2.3 <i>Регистр FCR</i> .....                                                   | 191 |

| 10.2.4 <i>Регистр LSR</i> .....                                                   | 191 |

| 10.2.5 <i>Регистр IER</i> .....                                                   | 193 |

| 10.2.6 <i>Регистр IIR</i> .....                                                   | 193 |

| 10.2.7 <i>Регистр MCR</i> .....                                                   | 195 |

| 10.2.8 <i>Регистр MSR</i> .....                                                   | 196 |

| 10.2.9 <i>Программируемый генератор скорости обмена</i> .....                     | 196 |

| 10.3 РАБОТА С FIFO ПО ПРЕРЫВАНИЮ .....                                            | 198 |

| 10.4 РАБОТА С FIFO ПО ОПРОСУ .....                                                | 199 |

| 11. ПОРТ ОБМЕНА ПОСЛЕДОВАТЕЛЬНЫМ КОДОМ .....                                      | 200 |

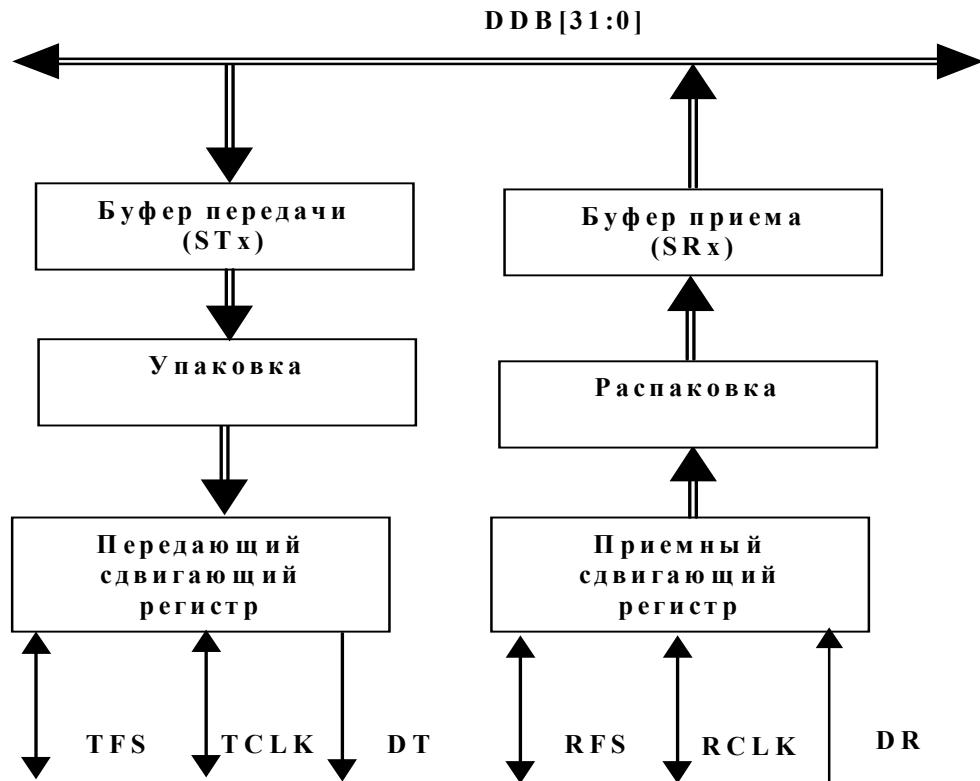

| 11.1 Общие положения .....                                                        | 200 |

| 11.2 Регистры.....                                                                | 202 |

| 11.2.1 <i>Общие положения</i> .....                                               | 202 |

| 11.2.2 <i>Буфер передачи STx</i> .....                                            | 202 |

| 11.2.3 <i>Буфер приема SRx</i> .....                                              | 203 |

| 11.2.4 <i>Регистр управления передачей данных STCTL</i> .....                     | 203 |

| 11.2.5 <i>Регистр управления приемом данных SRCTL</i> .....                       | 205 |

| 11.2.6 <i>Регистр коэффициентов деления при передаче данных TDIV</i> .....        | 207 |

| 11.2.7 <i>Регистр коэффициентов деления при приеме данных RDIV</i> .....          | 208 |

| 11.2.8 <i>Регистры выбора канала в многоканальном режиме</i> .....                | 208 |

| 11.2.9 <i>Регистры сравнения принимаемых данных в многоканальном режиме</i> ..... | 209 |

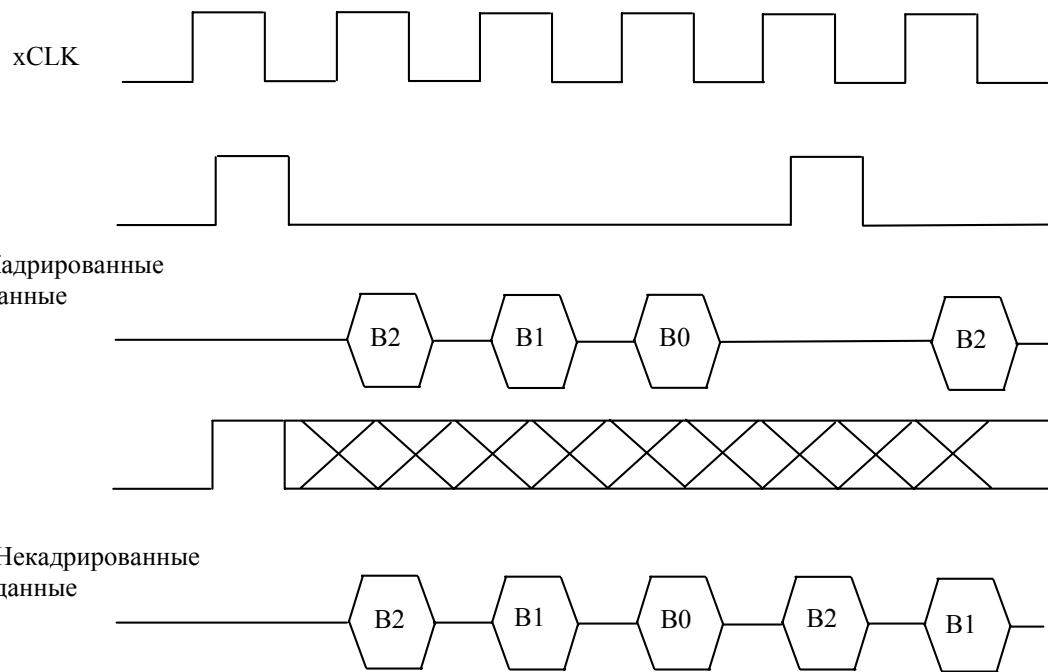

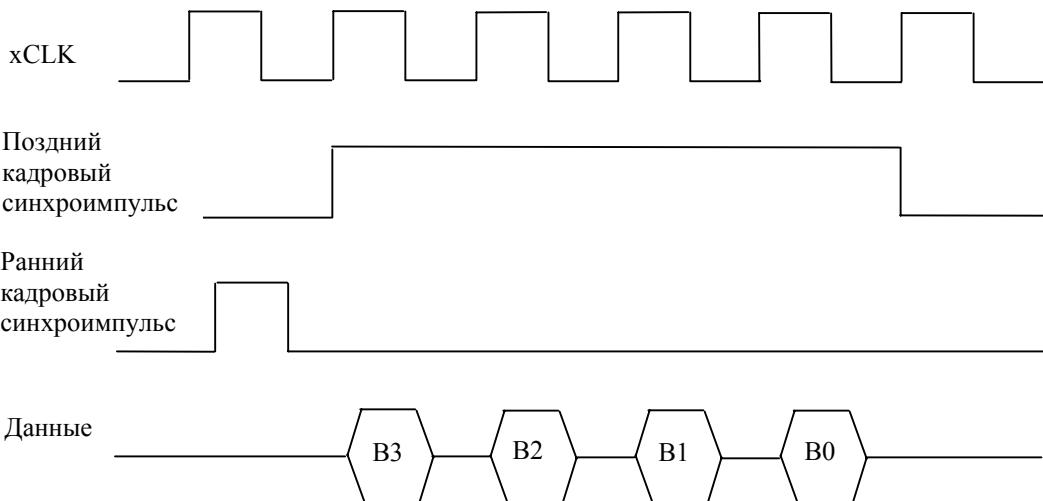

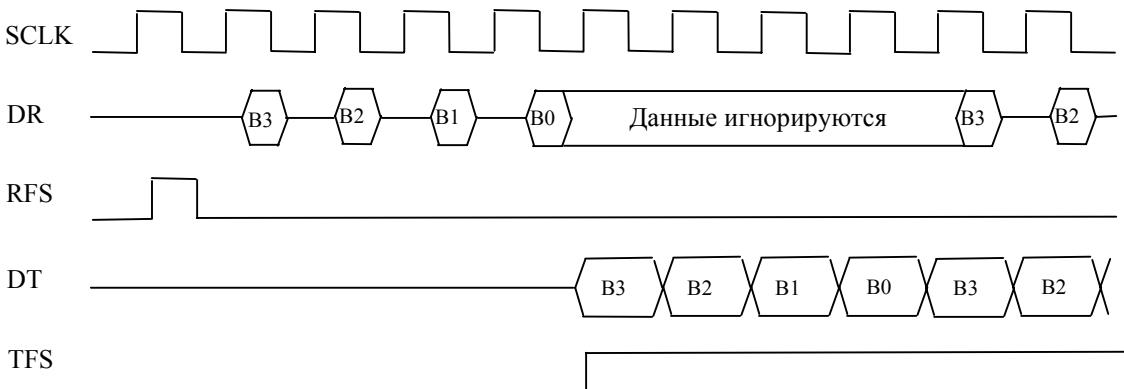

| 11.3 Одноканальный режим работы .....                                             | 209 |

| 11.4 Режим петли .....                                                            | 211 |

| 11.5 Многоканальный режим работы.....                                             | 212 |

| 11.6 DMA последовательного порта .....                                            | 214 |

| 11.7 Прерывания от последовательного порта .....                                  | 214 |

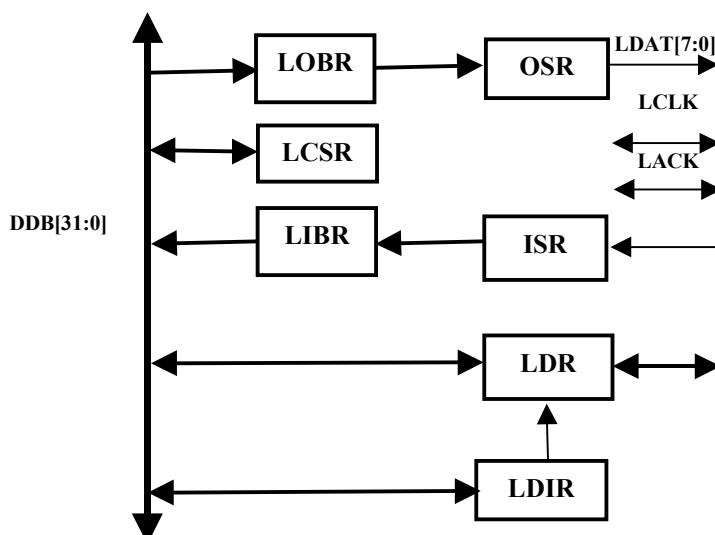

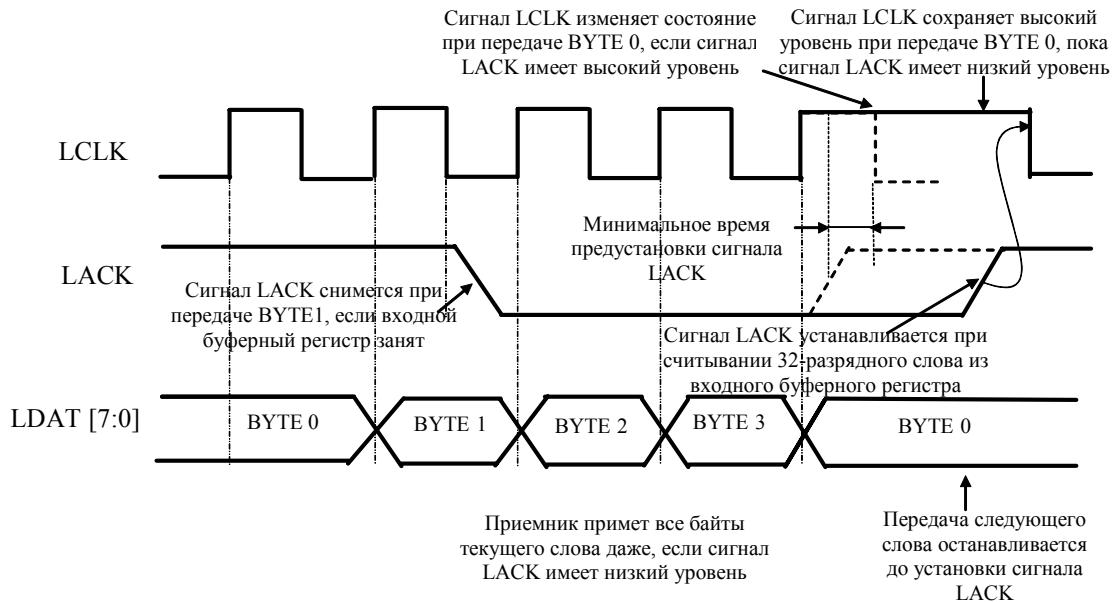

| 12. ЛИНКОВЫЙ ПОРТ .....                                                           | 215 |

| 12.1 Архитектура линкового порта .....                                            | 215 |

| 12.2 Регистры.....                                                                | 216 |

| 12.2.1 <i>Общие положения</i> .....                                               | 216 |

| 12.2.2 <i>Буфер передачи LTx</i> .....                                            | 216 |

| 12.2.3 <i>Буфер приема LRx</i> .....                                              | 217 |

| 12.2.4 <i>Регистр управления и состояния LCSR</i> .....                           | 217 |

| 12.2.5 <i>Регистры порта ввода-вывода</i> .....                                   | 218 |

| 12.3 DMA линковых портов.....                                                     | 218 |

| 12.4 Прерывания от линковых портов.....                                           | 218 |

| 12.4.1 <i>Прерывания при приеме и передаче данных</i> .....                       | 218 |

| 12.4.2 <i>Прерывания по запросу обслуживания</i> .....                            | 218 |

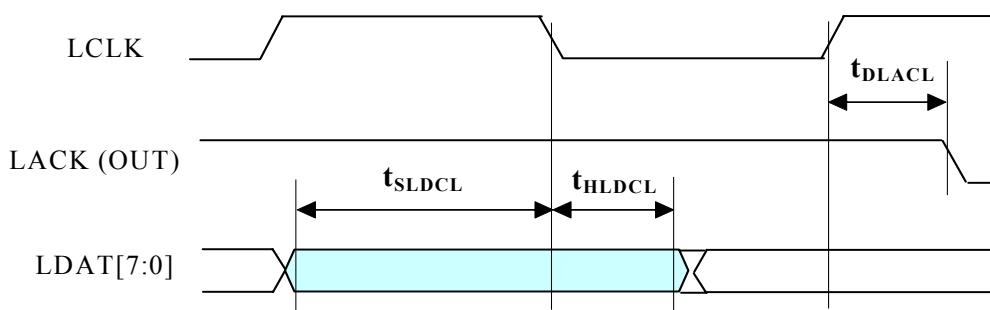

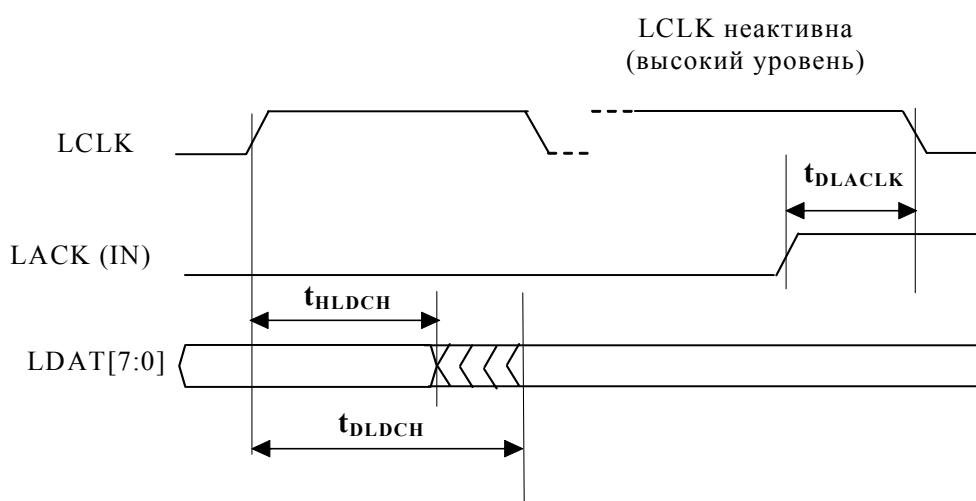

| 12.5 Временная диаграмма работы линкового порта .....                             | 219 |

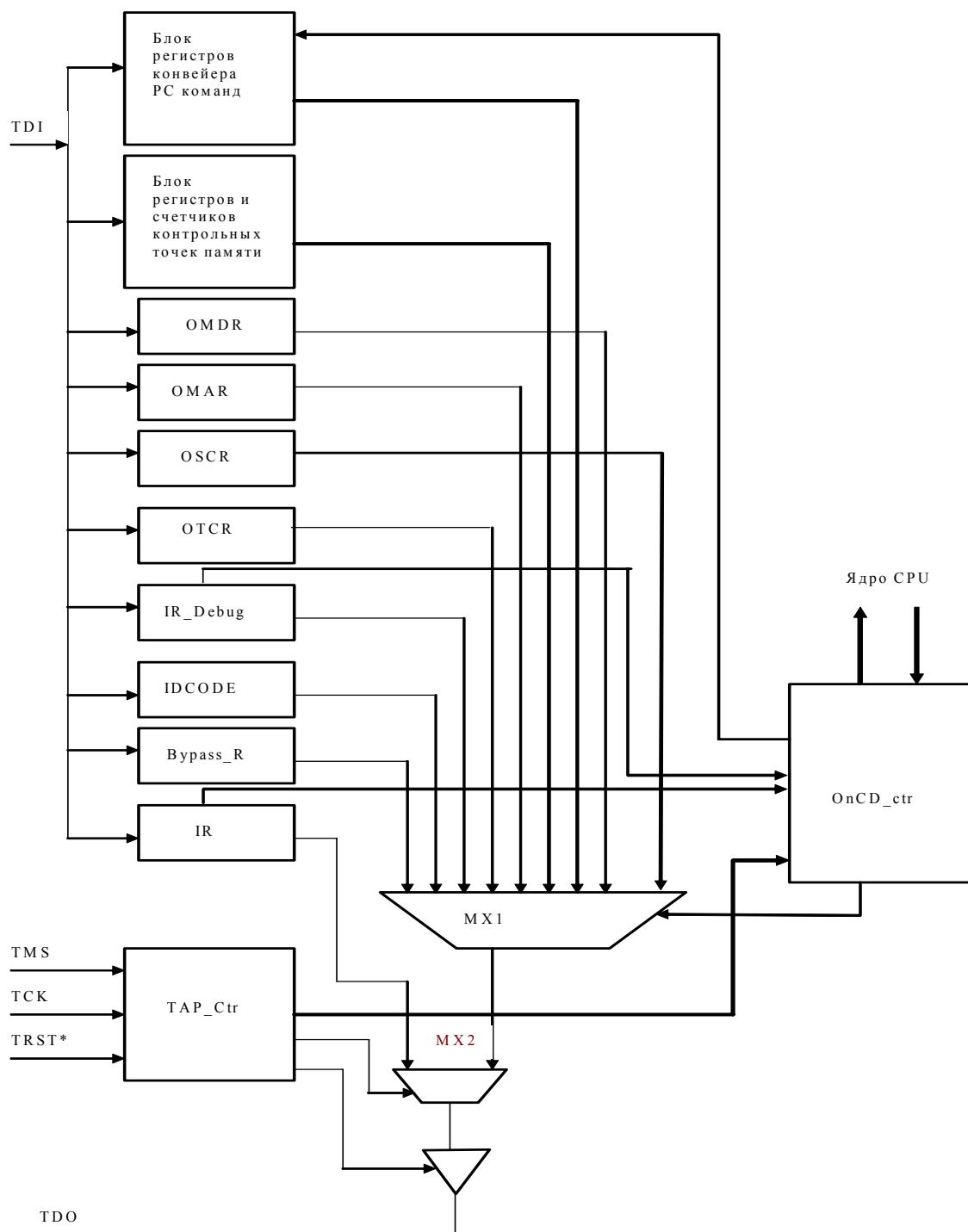

| 13. ПОРТ JTAG И ВСТРОЕННЫЕ СРЕДСТВА ОТЛАДКИ ПРОГРАММ.....                         | 220 |

| 13.1 Введение .....                                                               | 220 |

| 13.2 Порт JTAG .....                                                              | 222 |

| 13.2.1 <i>Внешние выводы порта</i> .....                                          | 222 |

| 13.2.2 <i>Контроллер порта (TAP)</i> .....                                        | 222 |

| 13.2.3 <i>Регистр команд (IR)</i> .....                                           | 222 |

| 13.2.4 <i>Регистр Bypass</i> .....                                                | 223 |

|                                                                                                                                      |     |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| 13.3 Модуль встроенных средств отладки программ (OnCD).....                                                                          | 223 |

| 13.3.1 Регистры модуля OnCD .....                                                                                                    | 223 |

| 13.3.1.1 Регистр команд OnCD (IRD) .....                                                                                             | 223 |

| 13.3.1.2 Регистр состояния и управления (OSCR) .....                                                                                 | 224 |

| 13.3.1.3 Счетчик трассы ОТС .....                                                                                                    | 225 |

| 13.3.1.4 Логическая организация контрольных точек останова .....                                                                     | 226 |

| 13.3.1.5 Информация о конвейере CPU .....                                                                                            | 227 |

| 13.3.1.6 Обмен данными с памятью MC-12 .....                                                                                         | 228 |

| 13.3.2 Способы перевода MC-12 в режим отладки.....                                                                                   | 228 |

| 13.3.2.1 Внешнее требование входа в режим отладки при действии сигнала nRST .....                                                    | 228 |

| 13.3.2.2 Внешнее требование входа в режим отладки во время нормальной работы MC-12 .....                                             | 228 |

| 13.3.2.3 Программный вход в режим отладки .....                                                                                      | 228 |

| 13.3.2.4 Переход в режим отладки после выполнения заданной трассы программы .....                                                    | 228 |

| 13.3.2.5 Вход в режим отладки после останова по контрольной точке в памяти и /или по PC .....                                        | 229 |

| 14. ЭЛЕКТРИЧЕСКИЕ И ВРЕМЕННЫЕ ПАРАМЕТРЫ .....                                                                                        | 230 |

| 14.1 ЭЛЕКТРОПИТАНИЕ .....                                                                                                            | 230 |

| 14.2 ЭЛЕКТРИЧЕСКИЕ ПАРАМЕТРЫ.....                                                                                                    | 230 |

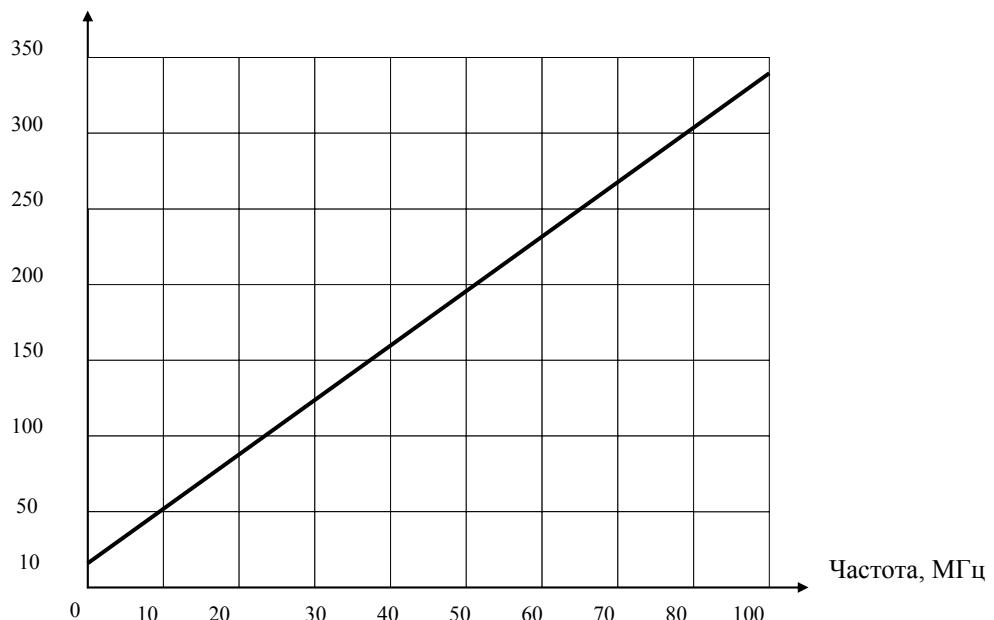

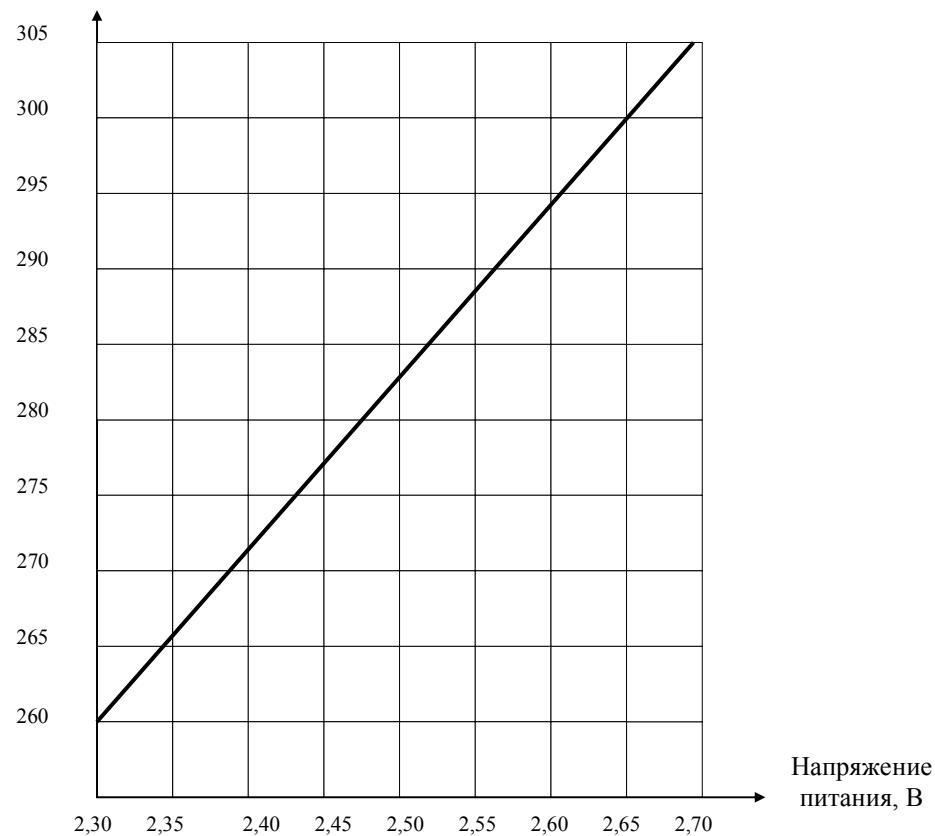

| 14.3 Динамическая потребляемая мощность .....                                                                                        | 231 |

| 14.4 ПРЕДЕЛЬНО-ДОПУСТИМЫЕ И ПРЕДЕЛЬНЫЕ ЭЛЕКТРИЧЕСКИЕ РЕЖИМЫ ЭКСПЛУАТАЦИИ .....                                                       | 232 |

| 14.5 ВРЕМЕННЫЕ ПАРАМЕТРЫ .....                                                                                                       | 233 |

| 14.5.1 Обмен данными с внешней памятью и устройствами .....                                                                          | 233 |

| 14.5.2 Прием и передача данных по линковому порту.....                                                                               | 234 |

| 14.5.3 Прием и передача данных по последовательному порту .....                                                                      | 236 |

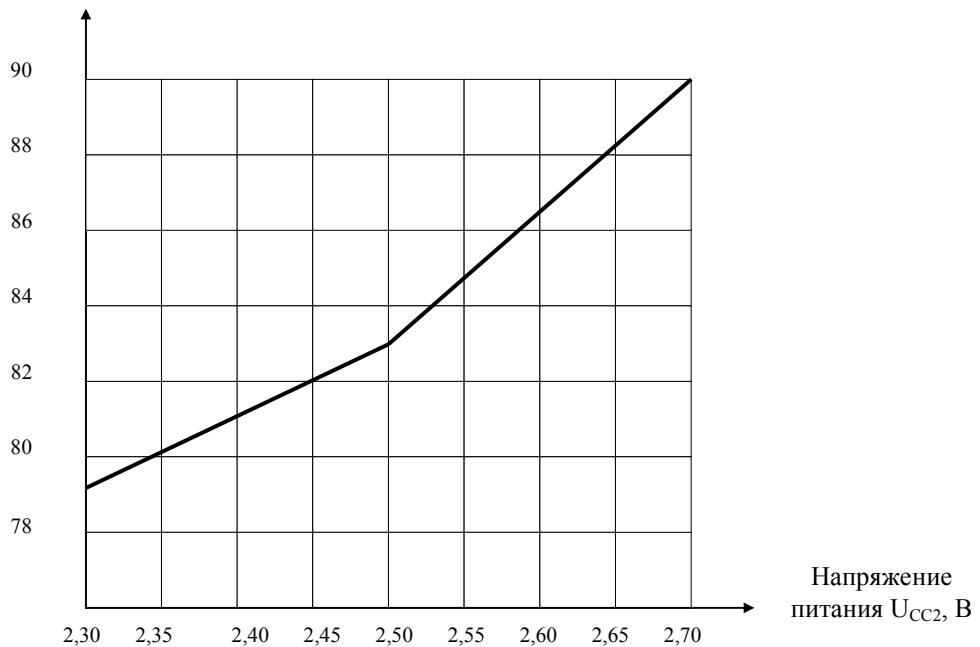

| 14.6 Зависимости основных параметров от режимов и условий эксплуатации.....                                                          | 237 |

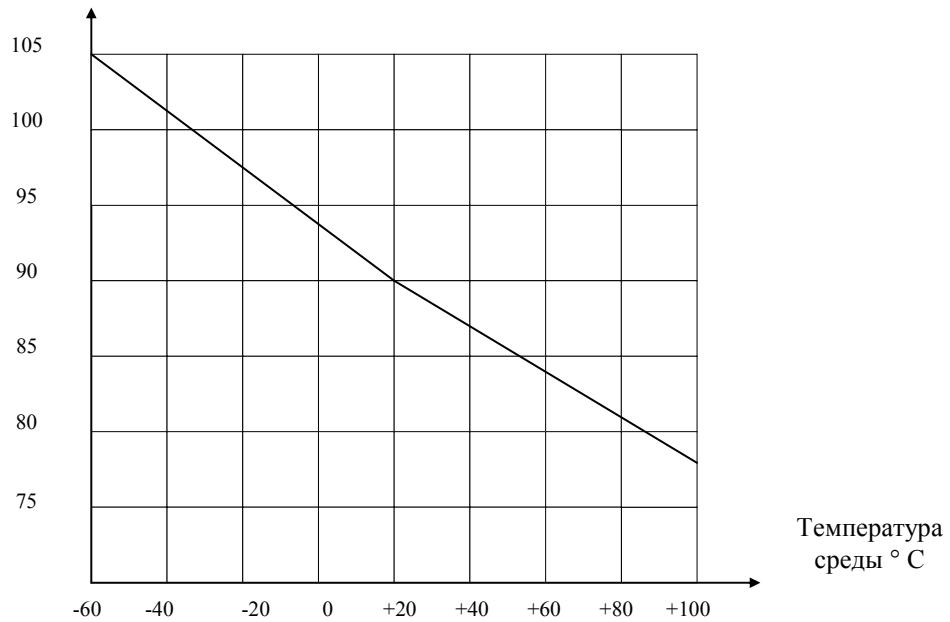

| 14.7 Рекомендации по подключению кварцевого резонатора .....                                                                         | 240 |

| 15. ОПИСАНИЕ ВНЕШНИХ ВЫВОДОВ .....                                                                                                   | 241 |

| 16. ИСТОРИЯ ИЗМЕНЕНИЙ .....                                                                                                          | 247 |

| 16.1 30 июня 2006 г .....                                                                                                            | 247 |

| • Уточнен подраздел 2.5 (Устройство управления памятью (MMU)).....                                                                   | 247 |

| • Уточнены п. 2.6.2, 2.7.3.10.....                                                                                                   | 247 |

| • Уточнены табл. 8.1 (бит INT_CTR), п. 8.2 и табл. 8.5 .....                                                                         | 247 |

| • Раздел 12 (Линковый порт): скорректированы табл. 12.1, 12.4, п. 12.4.1. Приведена временная диаграмма работы линкового порта ..... | 247 |

| • Скорректирован раздел 14. Приведены временные параметры .....                                                                      | 247 |

| • Уточнен раздел 15 в части назначения выводов .....                                                                                 | 247 |

| ПРИЛОЖЕНИЕ 1 .....                                                                                                                   | 248 |

| 1. ОБЩАЯ ХАРАКТЕРИСТИКА СИСТЕМЫ ИНСТРУКЦИЙ DSP-ЯДРА .....                                                                            | 249 |

| 1.1 Вычислительные команды .....                                                                                                     | 249 |

| 1.1.1 Команды сложения/вычитания в форматах с фиксированной точкой .....                                                             | 249 |

| 1.1.2 Команды умножения/накопления в форматах с фиксированной точкой .....                                                           | 250 |

| 1.1.3 Команды сдвига в форматах с фиксированной точкой.....                                                                          | 250 |

| 1.1.4 Другие арифметические команды в форматах с фиксированной точкой .....                                                          | 251 |

| 1.1.5 Округление, преобразования форматов, упаковка/распаковка .....                                                                 | 251 |

| 1.1.6 Логические команды, операции с битами и битовыми полями .....                                                                  | 252 |

| 1.1.7 Команды для обработки данных в формате 24E8 .....                                                                              | 252 |

| 1.1.8 Команды для обработки данных в формате 32E16 .....                                                                             | 253 |

| 1.1.9 Команды пересылок .....                                                                                                        | 253 |

| 1.1.10 Команды программного управления .....                                                                                         | 253 |

|                                                                                              |     |

|----------------------------------------------------------------------------------------------|-----|

| 1.2 ФОРМАТЫ ИНСТРУКЦИЙ .....                                                                 | 254 |

| 1.3 Алфавитный перечень команд.....                                                          | 255 |

| 1.4 Коды условия (CC) .....                                                                  | 260 |

| 1.5 Запись различных типов констант в операндах и памяти.....                                | 260 |

| 1.6 Поле выбора режима SCALING.....                                                          | 261 |

| 1.7 Ограничения при исполнении инструкций.....                                               | 262 |

| 1.7.1 Ограничение на адреса результатов одновременно исполняемых операций .....              | 262 |

| 1.7.2 Ограничения при исполнении инструкций программного управления.....                     | 262 |

| 1.7.3 Ограничения при исполнении инструкций пересылок .....                                  | 263 |

| ПРИЛОЖЕНИЕ 2.....                                                                            | 264 |

| ПРИМЕРЫ ПРОГРАММИРОВАНИЯ ДЛЯ МИКРОСХЕМЫ MC-12.....                                           | 264 |

| 1. КИХ - фильтр в прямой форме .....                                                         | 265 |

| 2. Деление $Y=Z/X$ (или обратная величина $Y=1/X$ ) .....                                    | 267 |

| 3. Сложение и умножение в Е-формате с плавающей точкой увеличенной разрядности $32E16$ ..... | 268 |

| 4. DCT-8 .....                                                                               | 269 |

| 5. Генераторы случайных величин .....                                                        | 269 |

| 6. Прямая циклическая автокорреляция .....                                                   | 270 |

| 7. Прямая КИХ-фильтрация .....                                                               | 270 |

| 8. Прямой КИХ-фильтр Гильберта .....                                                         | 271 |

| 9. Декодер Витерби .....                                                                     | 271 |

| 10. FFT, комплексное .....                                                                   | 272 |

# 1. ВВЕДЕНИЕ

## 1.1 Порядок использования данного документа

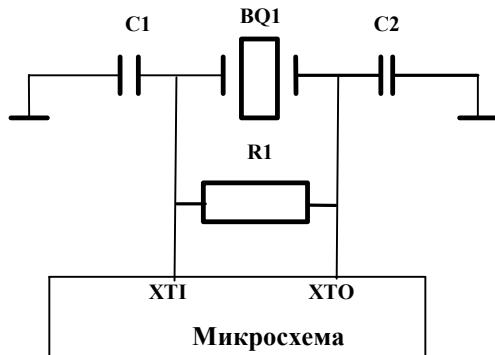

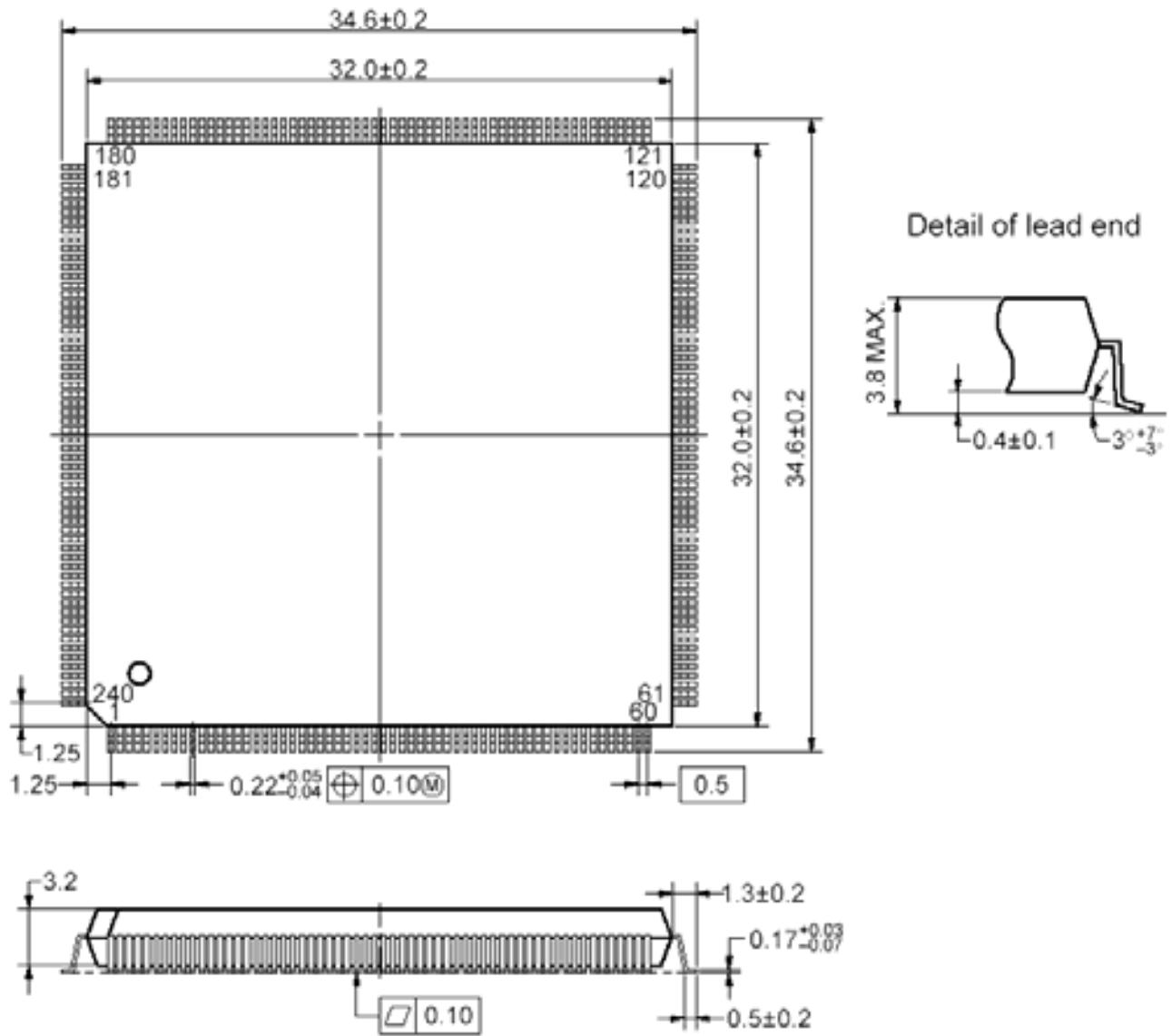

В данном документе рассмотрены вопросы архитектуры и функционирования микросхемы 1892ВМ3Т. Приведены ее электрические параметры, а также чертеж корпуса и назначение выводов. Рассмотрены вопросы типового включения микросхемы в систему и даны рекомендации по ее программированию.

Настоящая документация охраняется действующим законодательством Российской Федерации об авторском праве и смежных правах, в частности, законом Российской Федерации «Об авторском праве и смежных правах». ГУП НПЦ «ЭЛВИС» является единственным правообладателем исключительных авторских прав на настоящую документацию.

Настоящую документацию, не иначе как по предварительному согласию ГУП НПЦ «ЭЛВИС», запрещается:

- воспроизводить, т.е. изготавливать один или более экземпляров настоящей документации, ее части, в любой форме, любым способом;

- сдавать в прокат;

- публично показывать, исполнять или сообщать для всеобщего сведения,

- переводить;

- переделывать или другим образом перерабатывать (дорабатывать).

ГУП НПЦ «ЭЛВИС» оставляет за собой право в любой момент вносить изменения (дополнения) в настоящую документацию без предварительного уведомления о таком изменении (дополнении).

ГУП НПЦ «ЭЛВИС» не несет ответственности за вред, причиненный при использовании настоящей документации.

Передача настоящей документации не означает передачи каких-либо авторских прав ГУП НПЦ «ЭЛВИС» на нее.

Возникновение каких-либо прав на материальный носитель, на котором передается настоящая документация, не влечет передачи каких-либо авторских прав на данную документацию.

Все указанные в настоящей документации товарные знаки принадлежат их владельцам.

ГУП НПЦ «ЭЛВИС» ©, 2004

## 1.2 Назначение

Микросхема интегральная сигнального микроконтроллера 1892ВМ3Т спроектирована как однокристальная двухпроцессорная “система на кристалле” на базе IP-ядерной (IP-intellectual property) платформы «МУЛЬТИКОР», разработанной в ГУП НПЦ «ЭЛВИС».

Далее по тексту используется условное обозначение микросхемы 1892ВМ3Т как “MC-12”, где сокращение MC соответствует обозначению серии сигнальных контроллеров “**Мультикор(Multicore)**”, в которую входит микросхема 1892ВМ3Т.

По общепринятой классификации СБИС, разрабатываемых на базе платформы «МУЛЬТИКОР», MC-12 относится к сигнальным контроллерам мини-конфигурации с плавающей и фиксированной точкой.

В качестве двух процессоров MC-12 содержит 32-разрядный центральный процессор (CPU – Central Processing Unit) и высокопроизводительный процессор-акселератор для цифровой обработки сигналов (DSP – Digital Signal Processing) с плавающей/фиксированной точкой, обеспечивающий обработку информации с переменными форматами данных от битовых форматов до стандартных форматов данных с плавающей точкой в формате IEEE754.

Сигнальный контроллер MC-12 реализован на основе ядер из библиотеки платформы «МУЛЬТИКОР»: процессорного RISC - ядра **RISCore32** с архитектурой MIPS32 (CPU) и программируемого ядра с SISD (Single Instructions Single Data) архитектурой цифрового сигнального процессора (DSP) с плавающей/фиксированной точкой **ELcore-14™** (ELcore = Elvees's core).

MC-12 сочетает в себе лучшие качества двух классов приборов: микроконтроллеров и цифровых процессоров обработки сигналов, что особенно важно для микроминиатюрных встраиваемых применений, когда приходится решать в рамках ограниченных габаритов одновременно обе задачи: управления и высокоточной обработки информации, включая сигналы и изображение.

Для разработчика системы обеспечивается уникальная возможность применения новых алгоритмов принятия решений в CPU на основе параллельно выполняемых процедур адаптивного анализа и обработки сигналов в DSP, что реализуется в пределах одной и той же микросхемы, и что особенно важно для сверхминиатюрных применений. Для этих целей разработаны методы применения RLS/LNS алгоритмов на базе микросхем серий «МУЛЬТИКОР», в частности для адаптивных антенных решеток.

MC-12 обеспечивает работу под операционной системой **Linux**, а также под другими операционными системами для встраиваемых применений.

**MC-12 предназначен для применения в следующих приложениях:**

- Управление объектами с использованием высокоточных адаптивных методов;

- Высокоточная обработка данных для малогабаритных мобильных и встраиваемых систем;

- Системы промышленного контроля;

- Мультимедийная обработка изображений (JPEG 2000 и т.д.);

- Графические ускорители;

- Мультимедийная обработка звука (MPEG-1 Audio Layer3 [MP3], AMR, WMA, AAC и другие звуковые кодеки);

- Фильтрация, корреляция, быстрая свертка;

### 1.3 Функциональные параметры и возможности

Сигнальный микроконтроллер MC-12 имеет следующие функциональные параметры и возможности:

#### □ Центральный процессор (CPU):

- Архитектура – MIPS32;

- 32-х битные шины передачи адреса и данных;

- Кэш команд объемом 16 Кбайт;

- Архитектура привилегированных ресурсов в стиле ядра R4000:

- Регистры Count/Compare для прерываний реального времени;

- Отдельный вектор обработки исключений по прерываниям;

- Программируемое устройство управления памятью:

- Два режима работы – с TLB (Translation Lookaside Buffer) и FM (Fixed Mapped);

- 16 строк в режиме TLB.

- Устройство умножения и деления;

- JTAG IEEE 1149.1, встроенные средства отладки программ

- Производительность – 100 млн. оп/сек (здесь и далее параметры производительности приведены при тактовой частоте 100 МГц);

- Оперативная память центрального процессора (CRAM) объемом 64 Кбайт;

- 5 внешних запросов прерывания, в том числе немаскируемое прерывание (NMI).

#### □ Цифровой сигнальный процессор (DSP):

- “Гарвардская” RISC – подобная архитектура с оригинальной системой команд и преимущественно однотактным исполнением инструкций;

- **SISD (Single Instructions Single Data)** организация потоков команд и данных;

- Набор инструкций, совмещающий процедуры обработки и пересылки;

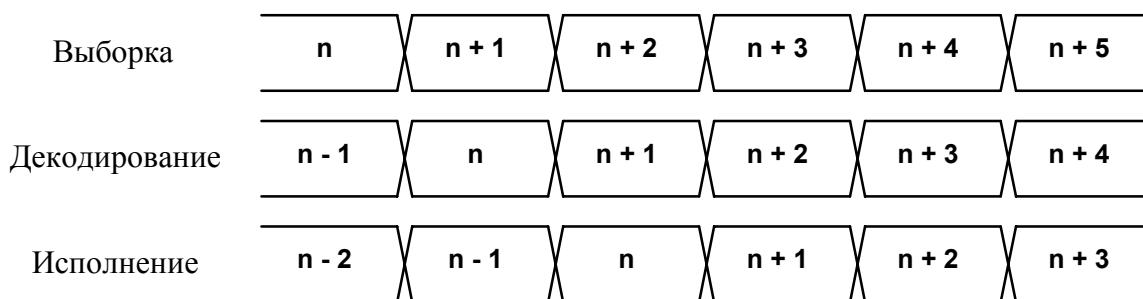

- 3-ступенчатый конвейер по выполнению 32– и 64–разрядных инструкций;

- Расширенные возможности по динамическому диапазону обрабатываемых данных, позволяющие обрабатывать данные в 8/16/32-разрядных форматах с фиксированной точкой, либо в одном из форматов с плавающей точкой – 24E8 (стандарт IEEE 754) или 32E16 (расширенный формат). Обеспечение при этом компромиссного выбора между точностью и производительностью. Аппаратные меры повышения точности и динамического диапазона (блочная плавающая точка; режим насыщения; инструкции преобразования форматов);

- Аппаратная поддержка программных циклов;

- Память программ PRAM объемом 16 Кбайт;

- Двухпортовые памяти данных XRAM и YRAM объемом 96 и 48 Кбайт соответственно;

- Пиковая производительность DSP:

- 300 млн. оп/с 32-битных операций с плавающей точкой (IEEE 754);

- 1800 млн. оп/с 8-битных операций с фиксированной точкой;

- 800 млн. оп/с 16-битных операций с фиксированной точкой;

- 400 млн. оп/с 32-битных операций с фиксированной точкой.

**□ Порт внешней памяти (MPORT):**

- Шина данных – 32 разряда, шина адреса – 32 разряда;

- Встроенный контроллер управления статической памятью типа SRAM, FLASH, ROM, а также синхронной памятью типа SDRAM;

- Программное конфигурирование типа блока памяти и его объема;

- Программное задание циклов ожидания;

- Формирование сигналов выборки 4 блоков внешней памяти;

- Обеспечение обслуживания 4 внешних прерываний.

**□ Периферийные устройства:**

- 12 - канальный контроллер прямого доступа в память (DMA). 4 внешних запроса прямого доступа; Специальные режимы синхронизации. Поддержка 2-мерной и разрядно-инверсной адресации. Режим передачи Flyby, подобный реализованному в ADSP-TS201: внешнее устройство  $\Leftrightarrow$  внешняя память;

- два порта обмена последовательным кодом (SPORT) совместимые с ADSP21160 (разработка фирмы ADI);

- четыре линковых порта (LPORT) совместимые с ADSP21160. Имеется режим работы в качестве портов ввода-вывода общего назначения (GPIO);

- универсальный асинхронный порт (UART) типа 16550;

- 32-разрядный интервальный таймер (IT);

- 32-разрядный таймер реального времени (RTT);

- 32-разрядный сторожевой таймер (WDT).

**□ Дополнительные возможности и особенности:**

- Узел фазовой автоподстройки частоты (PLL) с умножителем/делителем входной частоты;

- Встроенные средства отладки программ (OnCD);

- Порт JTAG в соответствии со стандартом IEEE 1149.1;

- Режимы энергосбережения;

- Поддержка операционной системы Linux;

В Таблице 1.1 приведены основные параметры быстродействия микросхемы MC-12 при нормальных условиях.

Таблица 1.1 Основные параметры быстродействия микросхемы MC-12 при нормальных условиях.

| Характеристика                                                                                                                      | Значение параметра |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| <b>Пиковая производительность (в количестве арифметических операций за 1 такт) для:</b>                                             |                    |

| • 1b целочисленного формата данных                                                                                                  | 64                 |

| • 8b целочисленного формата данных                                                                                                  | 18                 |

| • 16b целочисленного формата данных                                                                                                 | 8                  |

| • 32b целочисленного формата данных                                                                                                 | 5                  |

| • 32b формата данных с плавающей точкой (IEEE754)                                                                                   | 3                  |

| <b>Количество MAC - операций (умножение с накоплением) за 1 такт для:</b>                                                           |                    |

| • MAC 1*1+32, целочисленный 1b формат данных                                                                                        | 32                 |

| • MAC (8+j8)*(8+j8)+(32+j32), комплексный целочисленный 8b формат данных                                                            | 2                  |

| • MAC 16*16+32 , целочисленный 16b формат данных                                                                                    | 2                  |

| • MAC 32*32+64, целочисленный 32b формат данных                                                                                     | 1                  |

| • MAC32*32+32, формат 32b данных с плавающей точкой (IEEE754)                                                                       | 1                  |

| <b>Время выполнения операции сложения с плавающей точкой расширенного формата 32Е16, в тактах:</b>                                  |                    |

| • с нормализацией результата                                                                                                        | 5                  |

| • без нормализации результата                                                                                                       | 3                  |

| <b>Время выполнения операции вычитания с плавающей точкой расширенного формата 32Е16, в тактах:</b>                                 |                    |

| • с округлением                                                                                                                     | 6                  |

| • без округления                                                                                                                    | 5                  |

| • без нормализации результата                                                                                                       | 4                  |

| • без округления и нормализации                                                                                                     | 3                  |

| <b>Время выполнения операции сложения и вычитания одной пары операндов с плавающей точкой расширенного формата 32Е16, в тактах:</b> |                    |

| • с округлением                                                                                                                     | 9                  |

| • без округления                                                                                                                    | 8                  |

| • без нормализации результата                                                                                                       | 5                  |

| • без округления и нормализации                                                                                                     | 4                  |

| <b>Время выполнения операции умножения с плавающей точкой расширенного формата 32Е16, в тактах:</b>                                 | 4                  |

|                                                                                                                                                                        |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| • с нормализацией результата<br>• без нормализации результата                                                                                                          | 2        |

| <b>Нерекурсивная фильтрация, целочисленный формат 16*16+32:</b><br>• Производительность, число тактов на отвод<br>• Скалярная задержка                                 | 0.5<br>1 |

| <b>Нерекурсивная фильтрация, целочисленный формат 32*32+64:</b><br>• Производительность, число тактов на отвод<br>• Скалярная задержка                                 | 1<br>1   |

| <b>Нерекурсивная фильтрация, целочисленный комплексный формат (8+j8)*(8+j8)+(32+j32):</b><br>• Производительность, число тактов на отвод<br>• Скалярная задержка       | 0.5<br>1 |

| <b>Нерекурсивная фильтрация, целочисленный комплексный формат (16+j16)*(16+j16)+(32+j32):</b><br>• Производительность, число тактов на отвод<br>• Скалярная задержка   | 2<br>2   |

| <b>Нерекурсивная фильтрация, целочисленный комплексный формат (32+j32)*(32+j32)+(64+j64):</b><br>• Производительность, число тактов на отвод<br>• Скалярная задержка   | 4<br>4   |

| <b>Нерекурсивная фильтрация, комплексный формат плавающей точки (32+j32)*(32+j32)+(32+j32):</b><br>• Производительность, число тактов на отвод<br>• Скалярная задержка | 4<br>4   |

| <b>БПФ- 1024, комплексный формат данных и коэффициентов (16+j16), блочная плавающая точка</b>                                                                          | 11600    |

| <b>БПФ - 1024, комплексный формат плавающей точки, стандарт IEEE 754</b>                                                                                               | 21000    |

| <b>БПФ- 256, комплексный формат данных и коэффициентов (16+j16), блочная плавающая точка</b>                                                                           | 2400     |

| <b>БПФ - 256, комплексный формат плавающей точки, стандарт IEEE 754</b>                                                                                                | 4300     |

| <b>Декодер Витерби, на одну метрику пути, 16b формат</b>                                                                                                               | 1        |

| <b>БП Уолша – Адамара - 256, комплексное, формат (16+j16), блочная плавающая точка</b>                                                                                 | 1200     |

| <b>Деление (y/x), формат плавающей точки, стандарт IEEE 754 **)</b>                                                                                                    | 10       |

| <b>Обратная величина квадратному корню, формат плавающей точки, стандарт IEEE 754</b>                                                                                  | 12       |

***Примечания к табл. 1.1***

\*) Рабочая частота микросхемы при нормальной температуре - 100МГц

\*\*) От 2 до 10 тактов для деления и от 2 до 12 тактов для операции вычисления обратной величины квадратному корню, в зависимости от требуемой точности результата

**1.4 Структурная схема**

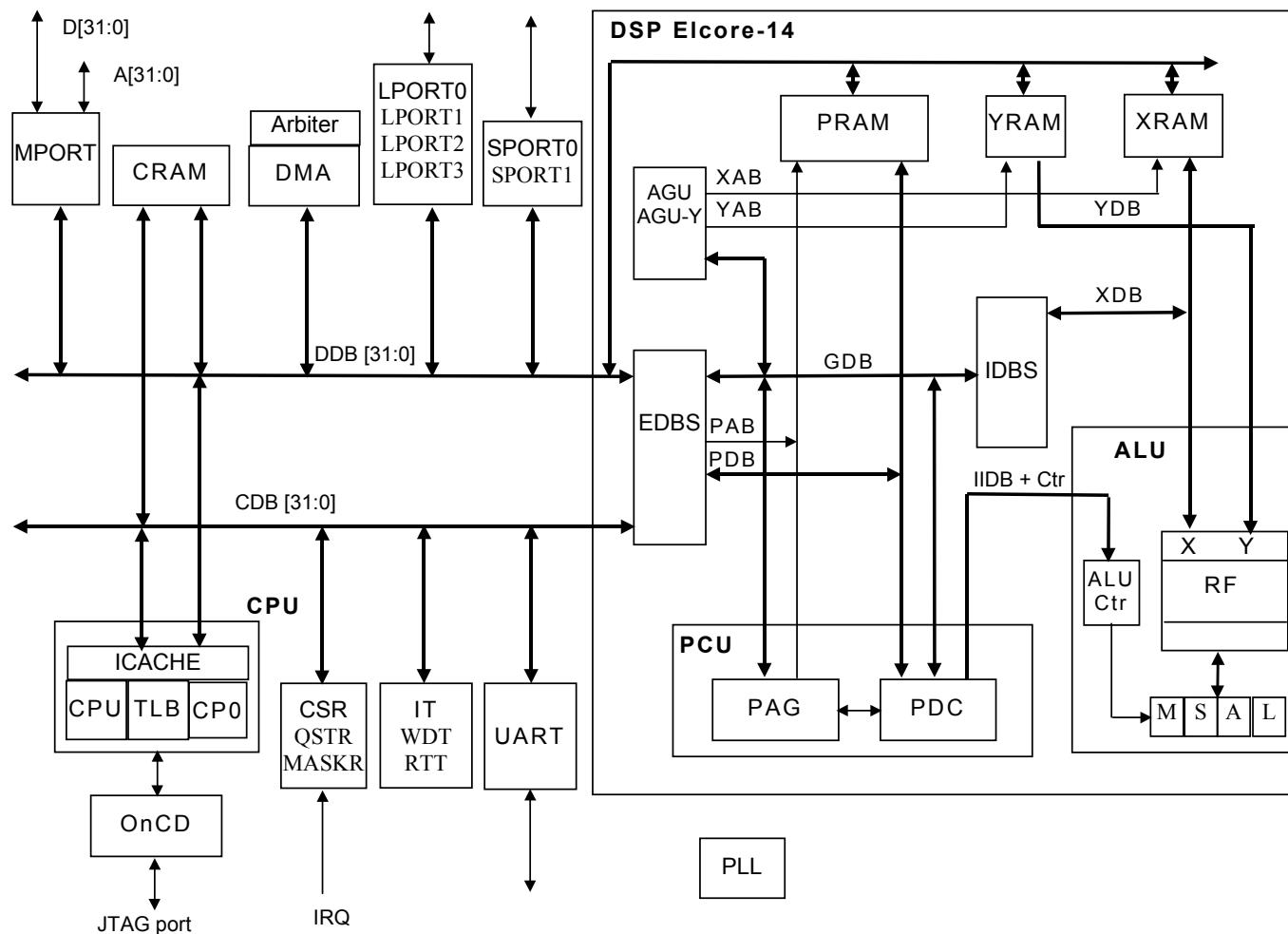

Структурная схема МС-12 приведена на Рисунок 1.1.

Рисунок 1.1. Структурная схема микросхемы MC-12

**В состав МС-12 входят следующие основные узлы и компоненты:**

- **CPU** – центральный процессор на основе RISC-ядра;

- **CRAM** – двухпортовая оперативная память центрального процессора;

- **DSP** – сопроцессор цифровой обработки сигналов с фиксированной точкой (далее может называться также **ЦПОС** – цифровой процессор обработки сигналов);

- **DMA** – контроллер прямого доступа в память;

- **MPORT** – порт внешней памяти;

- **SPORT** – последовательный порт;

- **LPORT** – линковый порт;

- **UART** – универсальный асинхронный порт;

- **ICACHE** – кэш программ центрального процессора;

- **IT** – интервальный таймер;

- **WDT** – сторожевой таймер;

- **RTT** – таймер реального времени;

- **CDB[31:0]** – шина данных CPU;

- **DDB[31:0]** – шина данных DMA;

- **A[31:0]** – шина адреса порта внешней памяти;

- **D[31:0]** – шина данных порта внешней памяти;

- **OnCD** – встроенные средства отладки программ;

- **XRAM, YRAM** – памяти данных DSP;

- **PRAM** – память программ DSP;

- **AGU** – адресный генератор;

- **EDBS** – коммутатор внешних шин;

- **IDBS** – коммутатор внутренних шин;

- **PCU** – устройство программного управления;

- **PAG** – генератор адреса программ;

- **PDC** – программный дешифратор;

- **RF** – регистровый файл;

- **ALU** – арифметическое устройство;

- **ALUCtr** – управление ALU;

- **XDB0 – XDB3, GDB, PDB** – шина данных DSP;

- **XAB, YAB, PAB** – адресные шины DSP;

- **M, S, A, L** – арифметические узлы ALU DSP.

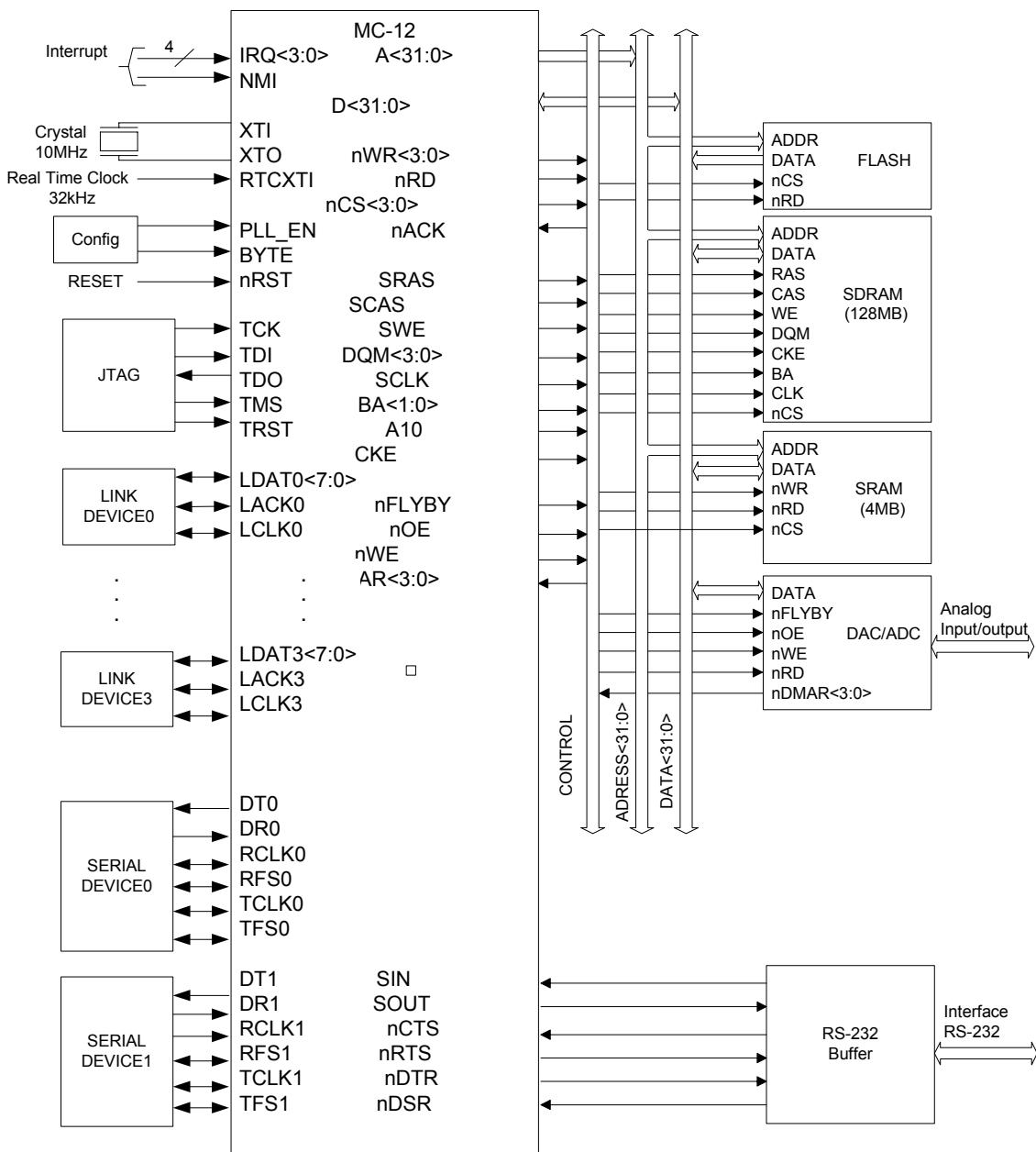

На Рисунке 1.2 приведена типовая схема применения МС-12.

Рисунок 1.2. Типовая схема применения MC-12

На Рисунке 1.2 использованы следующие обозначения:

- FLASH** – постоянное запоминающее устройство типа FLASH;

- SDRAM** – синхронное динамическое оперативное запоминающее устройство (ОЗУ);

- SRAM** – статическое ОЗУ;

- Interrupt** – запросы прерывания;

- DAC/ADC** – цифро-аналоговые и аналого-цифровые преобразователи;

- LINK DEVICE** – устройства, подключаемые к линковым портам;

- SERIAL DEVICE** – устройства, подключаемые к последовательным портам;

- RS-232 Buffer** – приемо-передатчики RS-232;

- Config** – схема задания конфигурации;

- RESET** – узел формирования сигнала установки исходного состояния.

## 1.5 Инструментальное программное обеспечение

Для микросхемы MC-12 разработана интегрированная среда проектирования программного обеспечения **MCStudio™**, которая обеспечивает полный цикл разработки и отладки программ.

MCS является кросс - системой и функционирует на инструментальной машине IBM PC в среде Windows 9x, XP.

### Интегрированная среда проектирования включает:

- среду разработки программ для RISC – и DSP - ядер;

- среду отладки программ в исходных текстах, исполняемых на программном симуляторе, и отладчик для работы с платой отладочного модуля (MC-12EM) для микросхемы MC-12 или целевым устройством через JTAG;

- средства программного моделирования;

- возможность доступа пользователю ко всем инструментам через один интерфейс.

### Среда разработки программ для RISC – ядра включает:

- компилятор с языка Си с препроцессором;

- ассемблер с препроцессором;

- дисассемблер;

- линковщик;

- библиотекарь;

- утилиты подготовки исполняемого кода.

### Среда разработки программ для ЦПОС – ядра включает:

- ассемблер с препроцессором;

- дисассемблер;

- линковщик;

- библиотекарь;

- утилиты подготовки исполняемого кода.

Описание интегрированной среды и инструментального программного обеспечения приведено в документации (см. раздел 1.7 «Дополнительная документация»).

В состав отладочного комплекта MC-12EM входят:

- Интегрированная среда разработки и отладки программ MCStudio<sup>TM</sup>;

- Отладочный модуль с JTAG-отладчиком;

- Набор кабелей и источник питания;

- Библиотека прикладных программ для DSP и MC-12 в целом (*Примечание. Поставляется как опция*).

Инструментальное программное обеспечение MC-12 базируется на архитектуре MIPS32. Вследствие этого, оно поддерживает большой объем свободно распространяемого программного обеспечения для этой архитектуры.

Библиотека прикладных программ для микросхемы MC-12 включает:

- программы БПФ комплексных и действительных чисел;

- программы быстрой свертки и корреляции посредством БПФ (перекрытие с накоплением);

- рекурсивные и не рекурсивные программы фильтрации данных;

- элементарные математические функции;

- арифметические операции над матрицами.

## 1.6 Операционная система для микросхемы MC-12.

**Linux** - свободно распространяемое ядро Unix-подобной операционной системы. Linux обладает всеми свойствами современной Unix-системы, включая полноценную многозадачность, развитую подсистему управления памятью и сетевую подсистему.

Ядро Linux, поставляемое вместе со свободно распространяемыми прикладными и системными программами образует полнофункциональную универсальную операционную систему. Большую часть базовых системных компонент Linux унаследовал от проекта GNU, целью которого является создание свободной микроядерной операционной системы с лицом Unix.

В качестве дополнительной опции для микросхемы MC-12 в составе отладочного модуля MC-12EM может быть портировано ядро операционной системы **Linux** версий 2.4.17, 2.4.25, 2.6, 5...

## 1.7 Дополнительная документация

Дополнительно при изучении данного руководства рекомендуется использовать следующие документы:

- Процессорное ядро RISCore32. Система команд;

- DSP-ядро ELcore\_x4. Система инструкций;

- Микросхемы интегральные 1892ВМ3Т. Технические условия главного конструктора (ТУ ГК). (АЕЯР.431280.418 ТУ. Проект);

- Интегрированная среда разработки и отладки программ MCStudio. Установка среды MCStudio. Руководство системного программиста. (РАЯЖ. 00004-01 32 01);

- Интегрированная среда разработки и отладки программ MCStudio. Пользовательский интерфейс. Руководство оператора. (РАЯЖ. 00004-01 34 01);

- Интегрированная среда разработки и отладки программ MCStudio. Руководство программиста (РАЯЖ. 00004-01 33 01);

- Интегрированная среда разработки и отладки программ MCStudio. Инструменты ядра ELcore. Руководство программиста. (РАЯЖ. 00004-01 33 03);

- Интегрированная среда разработки и отладки программ MCStudio. Инструменты RISCore32. Руководство программиста. (РАЯЖ. 00004-01 33 02).

## 2. ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР

### 2.1 Основные характеристики CPU

- Архитектура – MIPS32;

- 32-х битные пути передачи адреса и данных;

- Кэш команд объемом 16 Кбайт;

- Архитектура привилегированных ресурсов в стиле ядра R4000:

- Регистры Count/Compare для прерываний реального времени;

- Отдельный вектор обработки исключений по прерываниям;

- Программируемое устройство управления памятью:

- Два режима работы – с TLB (Translation Look aside Buffer) и FM (Fixed Mapped);

- 16 строк в режиме TLB;

- Устройство умножения и деления;

- Поддержка отладки JTAG.

### 2.2 Блок схема

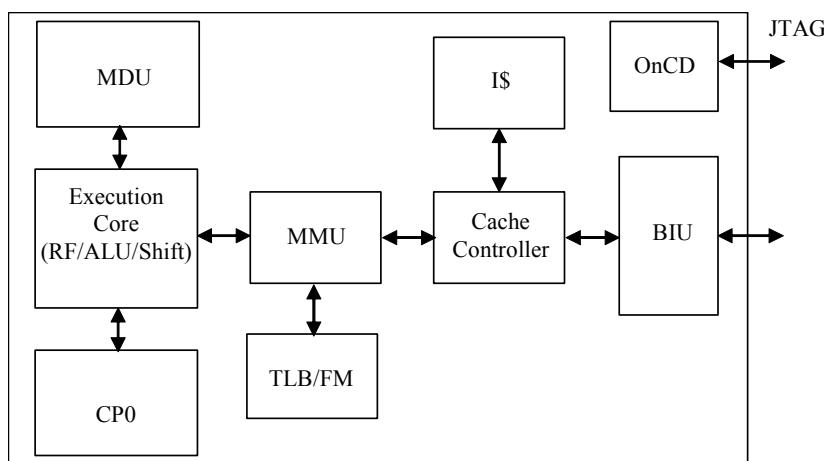

Блок схема процессорного ядра RISCore32 приведена на Рисунок 2.1.

Ядро содержит следующие узлы:

- Устройство исполнения (Execution Core);

- Устройство умножения и деления (MDU);

- Системный управляющий сопроцессор (CP0);

- Устройство управления памятью (MMU – Memory Management Unit);

- Контроллер кэш (Cache Controller);

- Устройство шинного интерфейса (BIU);

- Кэш команд (I\$);

- Средства отладки программ (OnCD – On Chip Debugger) с JTAG портом.

Рисунок 2.1. Блок схема процессорного ядра RISCore32

## 2.3 Составляющие логические блоки

В следующих подразделах описываются устройства, входящие в состав процессорного ядра.

### 2.3.1 Устройство исполнения

Входящее в ядро устройство исполнения реализует архитектуру load-store (загрузка-сохранение) с однотактными операциями арифметического логического устройства (АЛУ) (логические операции, операции сдвига, сложение и вычитание). В ядре имеется тридцать два 32-х битных регистра общего назначения, используемых для скалярных целочисленных операций и вычисления адреса. В регистровом файле есть два порта чтения и одинпорт записи. Также используются обходные пути передачи данных для минимизации количества остановок конвейера.

В состав устройства исполнения входят:

- 32-х битный сумматор, используемый для вычисления адреса данных;

- Адресное устройство для вычисления адреса следующей команды;

- Логика определения перехода и вычисления адреса перехода;

- Блок выравнивания при загрузке данных;

- Мультиплексоры обходных путей передачи данных для исключения остановок конвейера в тех случаях, когда команды, производящие данные и команды, использующие эти данные, расположены в программе достаточно близко;

- Блок обнаружения Нуля/Единицы для реализации команд CLZ и CLO;

- АЛУ для выполнения побитных операций;

- Сдвигающее устройство и устройство выравнивания при сохранении данных.

### 2.3.2 Устройство умножения/деления (MDU)

Устройство умножения/деления выполняет соответствующие операции. MDU выполняет операции умножения за 17 тактов, операции умножения с накоплением за 18 тактов, операции деления за 33 такта и операции деления с накоплением за 34 такта. Попытка активизировать следующую команду умножения/деления до завершения выполнения предыдущей, так же как и использование результата этой операции до того, как она закончена, вызывает остановку конвейера. В MDU имеется вывод, определяющий формат операции – знаковый или беззнаковый.

### 2.3.3 Системный управляющий сопроцессор

Сопроцессор отвечает за преобразование виртуального адреса в физический, протоколы кэш, систему управления исключениями, выбор режима функционирования (Kernel/User) и за разрешение/запрещение прерываний. Конфигурационная информация доступна посредством чтения регистров CR0 (см. раздел 2.7 “Регистры CR0”).

### 2.3.4 Устройство управления памятью (MMU)

Процессорное ядро содержит устройство управления памятью (MMU), реализующее интерфейс между исполнительным блоком и контроллером кэш. Ядро может работать как в режиме TLB – с 16-строчной, полностью ассоциативной матрицей TLB, так и в режиме FM (Fixed Mapped), когда используются простые преобразования виртуального адреса в физический адрес. Полностью устройство MMU описано в п. 2.5.

### 2.3.5 Контроллер кэш

В данной версии процессора реализован кэш команд, виртуально индексируемый и контролируемый по физическому тэгу типа direct mapped, что позволяет осуществлять доступ к кэш параллельно с преобразованием виртуального адреса в физический адрес. Объем кэш памяти составляет 16 Кбайт.

### 2.3.6 Устройство шинного интерфейса (BIU – Bus Interface Unit)

Устройство шинного интерфейса управляет внешними интерфейсными сигналами в соответствии со спецификацией шины AHB (Advanced High-performance Bus) архитектуры AMBA (Advanced Microcontroller Bus Architecture).

### 2.3.7 OnCD контроллер

В ядре имеется устройство для отладки программ OnCD с портом JTAG.

## 2.4 Конвейер

В RISC-ядре процессора реализован конвейер, состоящий из пяти стадий и аналогичный конвейеру ядра R3000. Конвейер дает возможность процессору работать на высокой частоте, при этом минимизируется сложность устройства, а также уменьшается стоимость и потребление энергии.

В этой главе содержатся следующие разделы:

- Раздел 2.1, “Стадии работы конвейера”

- Раздел 2.2, “Операции умножения и деления”

- Раздел 2.3, “Задержка выполнения команд перехода”

- Раздел 2.4, “Обходные пути передачи данных (Data bypass)”

- Раздел 2.5, “Задержка загрузки данных”

- Раздел 2.6, “Особые случаи при выполнении команд (Instruction Hazards)”

### 2.4.1 Стадии конвейера

Конвейер содержит пять стадий:

- Выборка команды (стадия I- Instruction)

- Дешифрация команды (стадия D - Data)

- Исполнение команды (стадия E - Execution)

- Выборка из памяти (стадия M - Memory)

- Обратная запись (стадия W – Write Back)

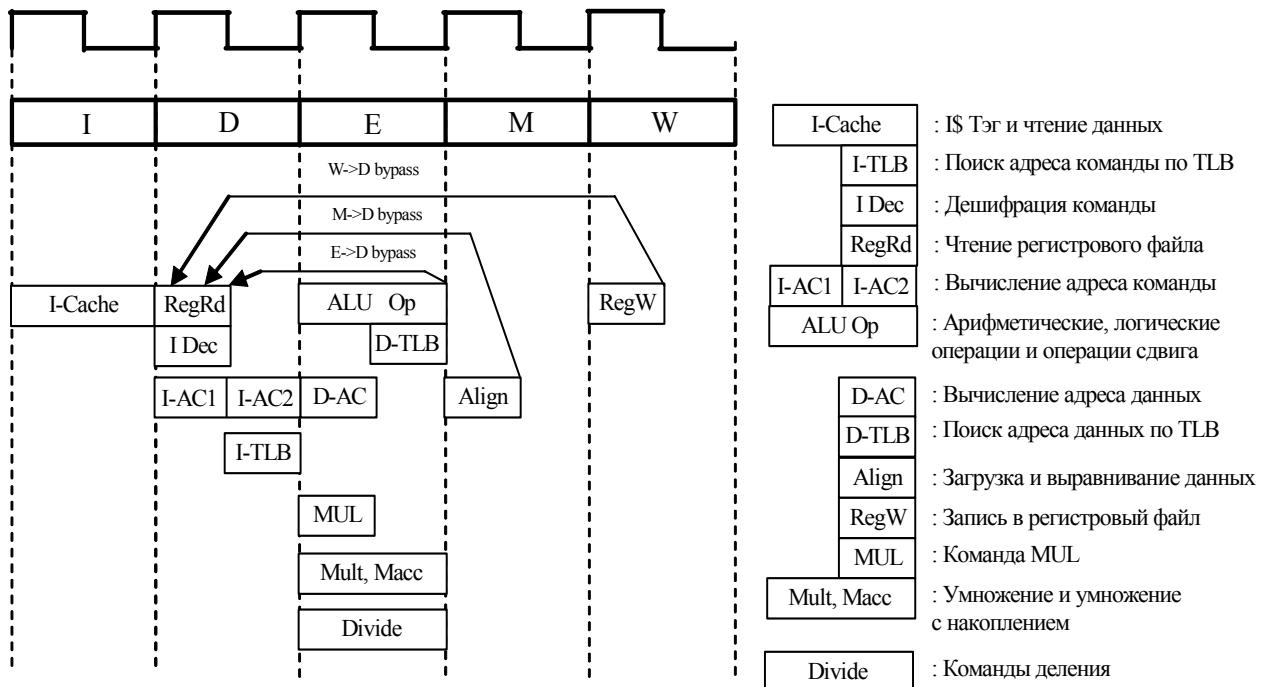

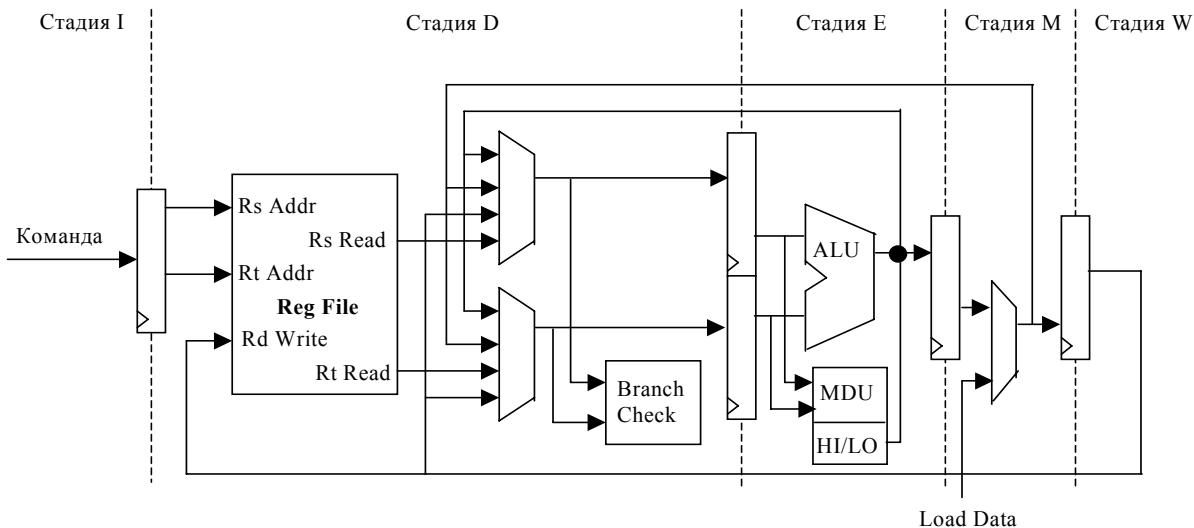

На Рисунок 2.2 показаны операции, выполняемые RISC-ядром на каждом этапе конвейера.

Рисунок 2.2

#### 2.4.1.1 Стадия I: выборка команды

На этой стадии команда выбирается из командного кэш.

#### 2.4.1.2 Стадия D: дешифрация команды

На этой стадии:

- Операнды выбираются из регистрового файла.

- Операнды передаются на эту стадию со стадий Е, М и В.

- ALU определяет, выполняется ли условие перехода и вычисляет виртуальный адрес перехода для команд перехода.

- Осуществляется преобразование виртуального адреса в физический адрес.

- Производится поиск адреса команды по TLB и вырабатывается признак hit/miss.

- Командная логика выбирает адрес команды.

#### 2.4.1.3 Стадия Е: исполнение

На этой стадии:

- ALU выполняет арифметические или логические операции для команд типа регистр-регистр.

- Производится преобразование виртуального адреса в физический адрес для данных, используемых командами загрузки и сохранения.

- Производится поиск данных по TLB и вырабатывается признак hit/miss.

- Все операции умножения и деления выполняются на этой стадии.

#### 2.4.1.4 Стадия M: выборка из памяти

На этой стадии осуществляется загрузка и выравнивание загруженных данных в границах слова.

#### 2.4.1.5 Стадия W: обратная запись

На этой стадии для команд типа регистр-регистр или для команд загрузки результат записывается обратно в регистровый файл.

### 2.4.2 Операции умножения и деления

Время выполнения этих операций соответствует 17 тактам для команд умножения и 18 тактам для команд умножения с накоплением, а также 33 тактам для команд деления и 34 тактам для команд деления с накоплением.

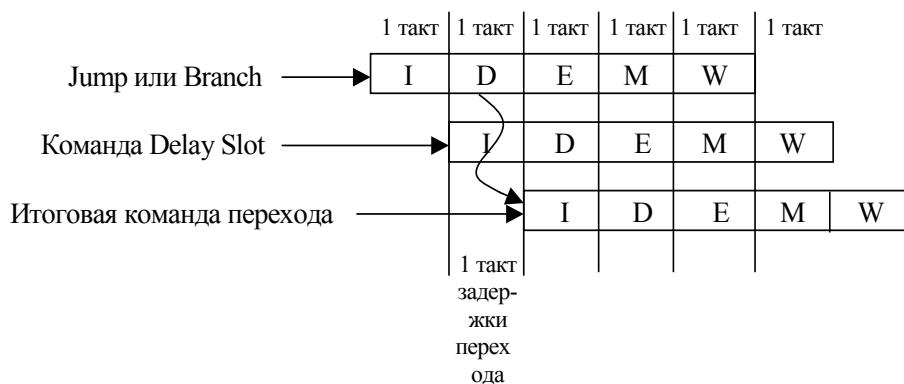

### 2.4.3 Задержка выполнения команд перехода (Jump, Branch)

Конвейер осуществляет выполнение команд перехода с задержкой в один такт. Однотактная задержка является результатом функционирования логики, ответственной за принятие решения о переходе на стадии D конвейера. Эта задержка позволяет использовать адрес перехода, вычисленный на предыдущей стадии, для доступа к команде на следующей D-стадии. Слот задержки перехода (branch delay slot) позволяет отказаться от остановок конвейера при переходе. Вычисление адреса и проверка условия перехода выполняются одновременно на стадии D. Итоговое значение PC (счетчика команд) используется для выборки очередной команды на стадии I, которая является второй командой после перехода. На Рисунок 2.3 показан слот задержки перехода.

Рисунок 2.3. Слот задержки перехода

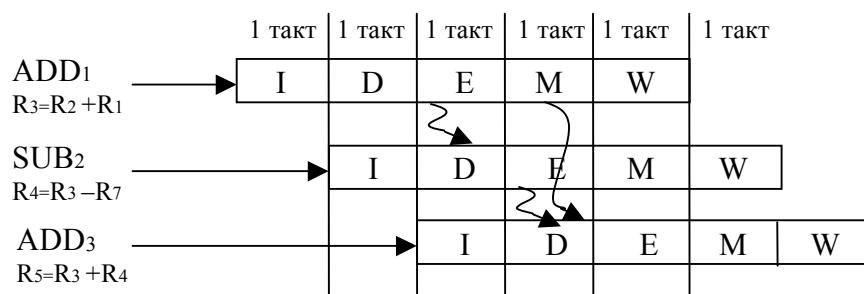

### 2.4.4 Обходные пути передачи данных (Data bypass)

Для большинства команд MIPS32 исходными operandами являются значения, хранящиеся в регистрах общего назначения. Эти operandы выбираются из регистрового файла в первой половине D-стадии. После исполнения на ALU результат, в принципе, готов для использования другими командами. Но запись результата в регистровый файл осуществляется только на стадии W. Это лишает следующую команду возможности использовать результат в течение 3-х циклов, если ее operandом является результат выполнения последней операции, сохраненный в регистровом файле. Для преодоления этой проблемы используются обходные пути передачи данных.

Мультиплексоры обходных путей передачи данных для обоих операндов располагаются между регистровым файлом и ALU (Рисунок 2.4). Они позволяют передавать данные с выхода стадий E, M и W конвейера прямо на стадию D, если один из регистров источника (source) декодируемой команды совпадает с регистром назначения (target) одной из предшествующих команд. Входы мультиплексоров подключены к обходным путям M→D и E→D, а также W→D.

Рисунок 2.4

На Рисунок 2.5 показаны обходные пути передачи данных для команды Add<sub>1</sub>, за которой следует команда Sub<sub>2</sub> и затем снова Add<sub>3</sub>. Поскольку команда Sub<sub>2</sub> в качестве одного из операндов использует результат операции Add<sub>1</sub>, используется обходной путь E→D. Следующая команда Add<sub>3</sub> использует результаты обеих предшествующих операций: Add<sub>1</sub> и Sub<sub>2</sub>. Так как данные команды Add<sub>1</sub> в это время находятся на стадии M, используется обходной путь M→D. Кроме того, вновь используется обходной путь E→D для передачи результата операции Sub<sub>2</sub> команде Add<sub>3</sub>.

Рисунок 2.5

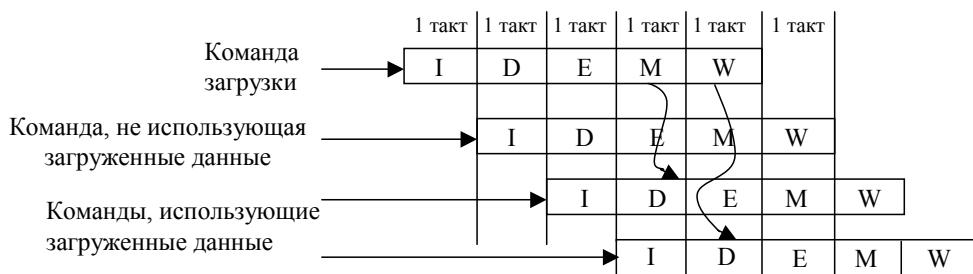

#### 2.4.5 Задержка загрузки данных

Данные, выбираемые командами загрузки (Load), становятся доступными на конвейере только после выравнивания на стадии M. При этом данные, являющиеся исходными operandами, должны предоставляться командам для обработки уже на стадии D. Поэтому, если сразу за командой загрузки следует команда, для которой один из регистров исходных operandов совпадает с регистром, в который производится загрузка дан-

ных, это вызывает приостановку в работе конвейера на стадии D. Эта приостановка осуществляется аппаратной вставкой команды NOP. Во время этой задержки часть конвейера, которая находится дальше стадии D, продолжает продвигаться. Если же команда, использующая загружаемые данные, следует за командой загрузки не сразу, а через одну или через две, то для обеспечения бесперебойной работы конвейера используется один из обходных путей передачи данных: M→D или W→D (Рисунок 2.6).

Рисунок 2.6

## 2.5 Устройство управления памятью (MMU)

### 2.5.1 Введение

Процессорное ядро содержит устройство управления памятью (MMU), реализующее интерфейс между устройством исполнения и контроллером кэш. MMU преобразует виртуальный адрес в физический прежде, чем посыпает запрос контроллеру кэш для сравнения тэга или блоку шинного интерфейса для доступа к внешнему запоминающему устройству. Это преобразование является очень полезным свойством функционирования операционных систем при управлении физической памятью таким образом, чтобы в ней размещались несколько процессов, активных в одной и той же области памяти, и может быть даже на одном виртуальном адресе, но обязательно в различных областях физической памяти. Другие свойства MMU - защита зон памяти и определение протокола кэш.

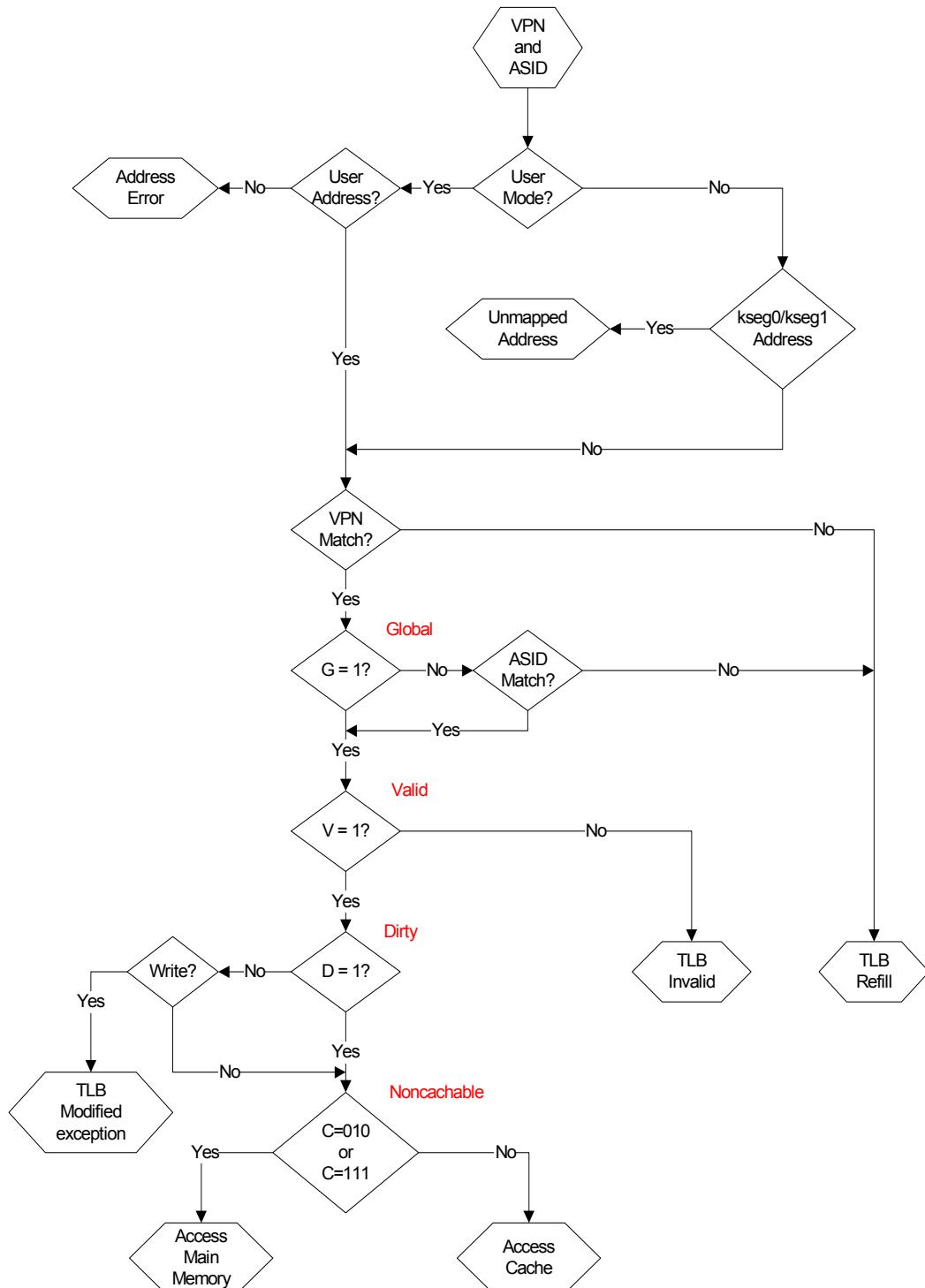

MMU может выполнять преобразование адресов в двух режимах: в режиме TLB и в режиме FM. Режим преобразования определяется битом FM регистра CSR.

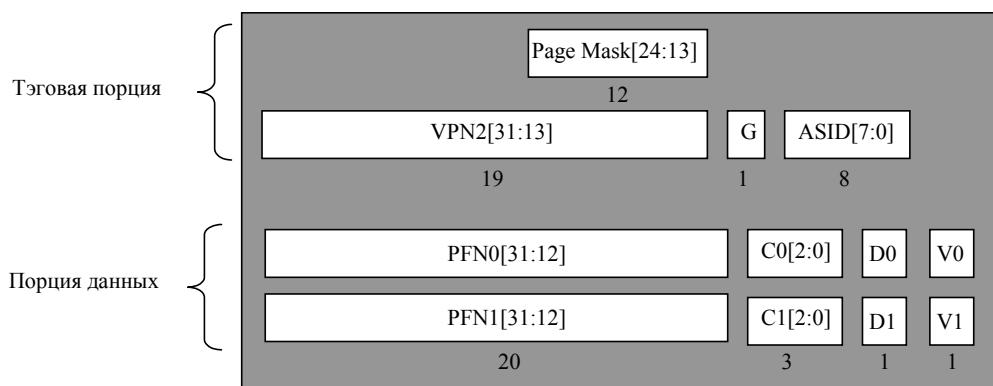

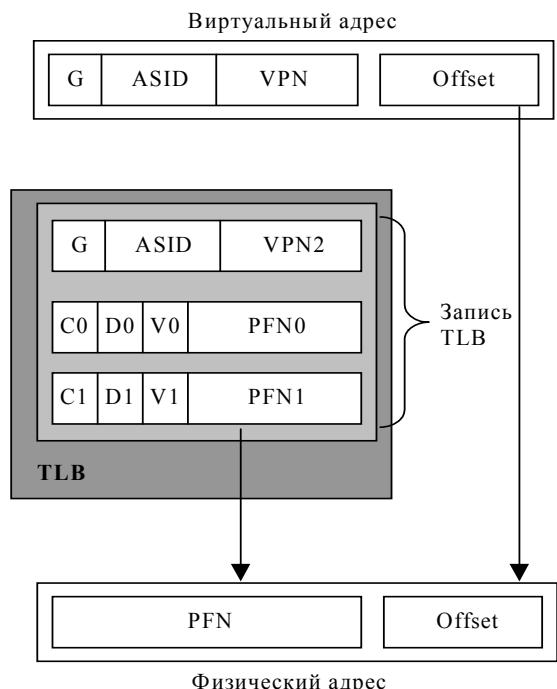

В режиме TLB используется полностью ассоциативная таблица преобразования адресов (TLB), имеющая 16 парных строк (entries). Во время преобразования осуществляется поиск соответствия по TLB. Если искомая строка отсутствует, генерируется прерывание.

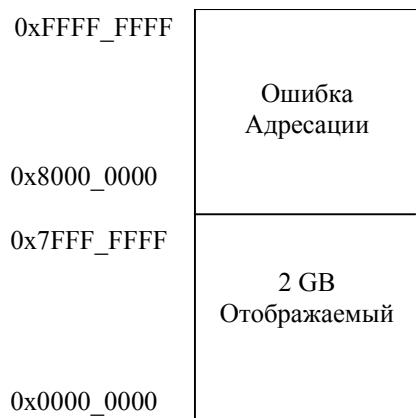

В режиме FM (Fixed Mapped) работа MMU основана на простом алгоритме, обеспечивающем преобразование виртуального адреса в физический посредством механизма фиксированного отображения. Правила преобразования отличаются для различных областей виртуального адресного пространства (useg/kuseg, kseg0, kseg1, kseg2, kseg3).

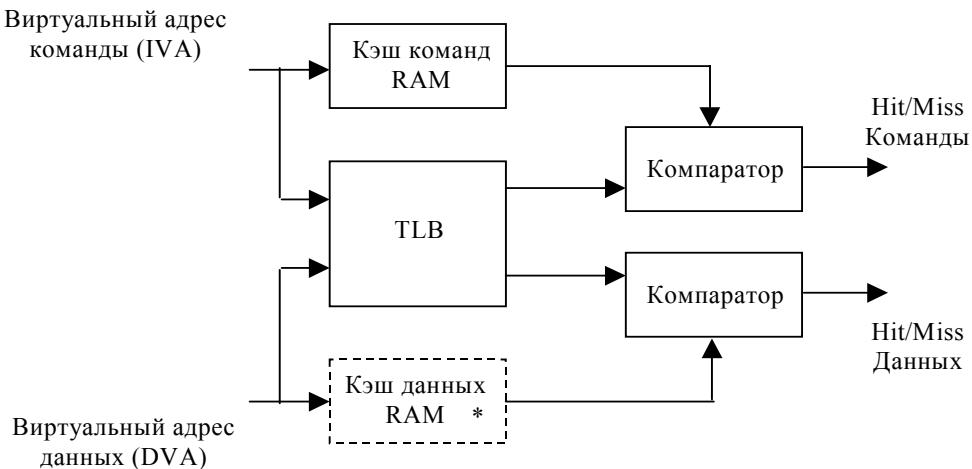

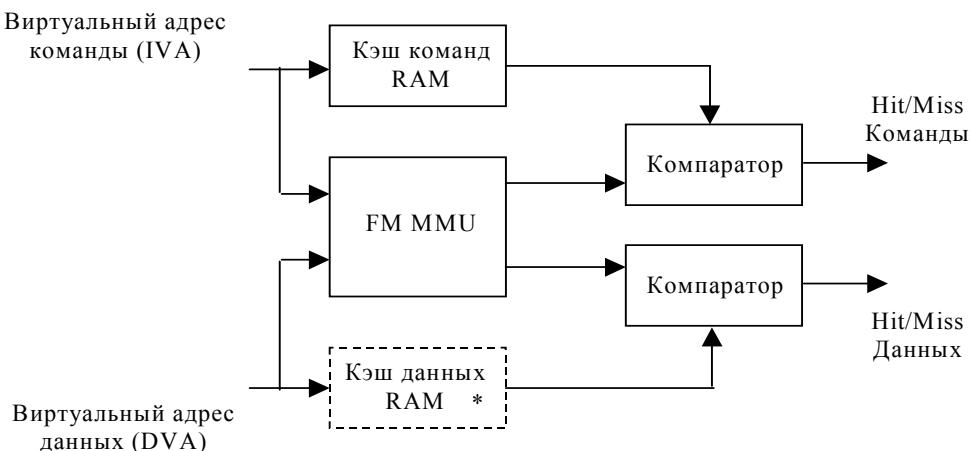

На Рисунок 2.7 показано, взаимодействие MMU с процедурой доступа к кэш в режиме TLB, а на Рисунок 2.8 – в режиме FM.

\* - Кэш данных в данной реализации отсутствует

Рисунок 2.7

\* - Кэш данных в данной реализации отсутствует

Рисунок 2.8

## 2.5.2 Режимы работы.

Процессорное ядро поддерживает два режима работы:

- Режим User (непrivилегированный режим)

- Режим Kernel (privилегированный режим)

Режим User в основном используется для прикладных программ. Режим Kernel обычно используется для обработки исключительных ситуаций и привилегированных функций операционной системы, включая управление сопроцессором СР0 и доступ к устройствам ввода-вывода.

Преобразования, выполняемые MMU, зависят от режима работы процессора.

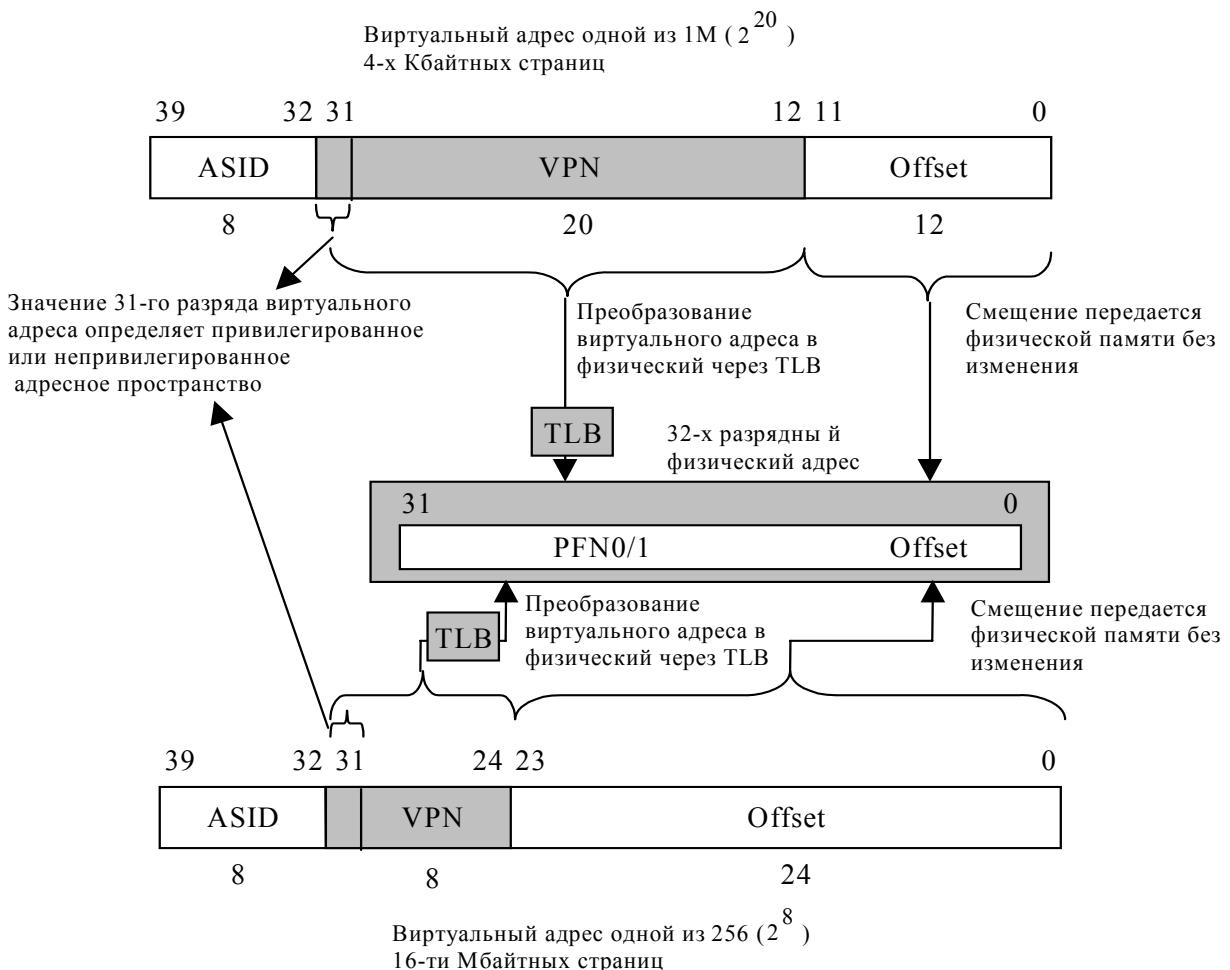

### 2.5.2.1 Виртуальные сегменты памяти

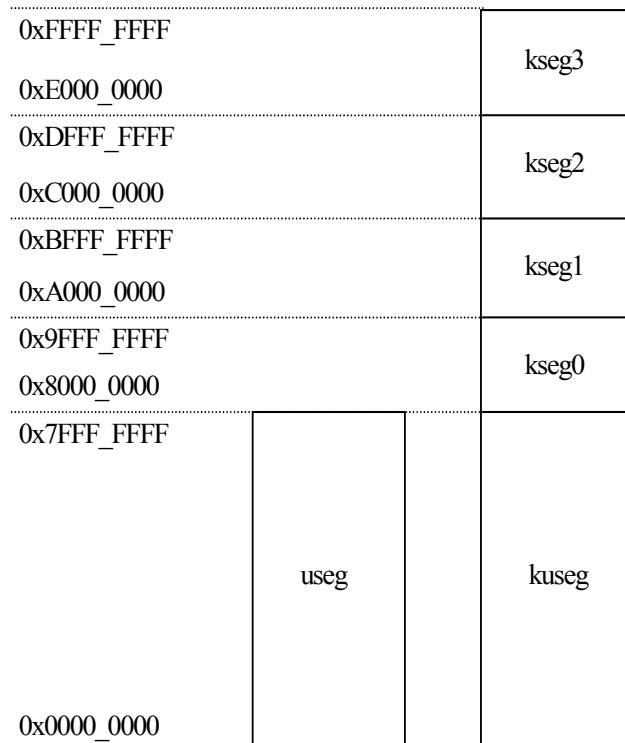

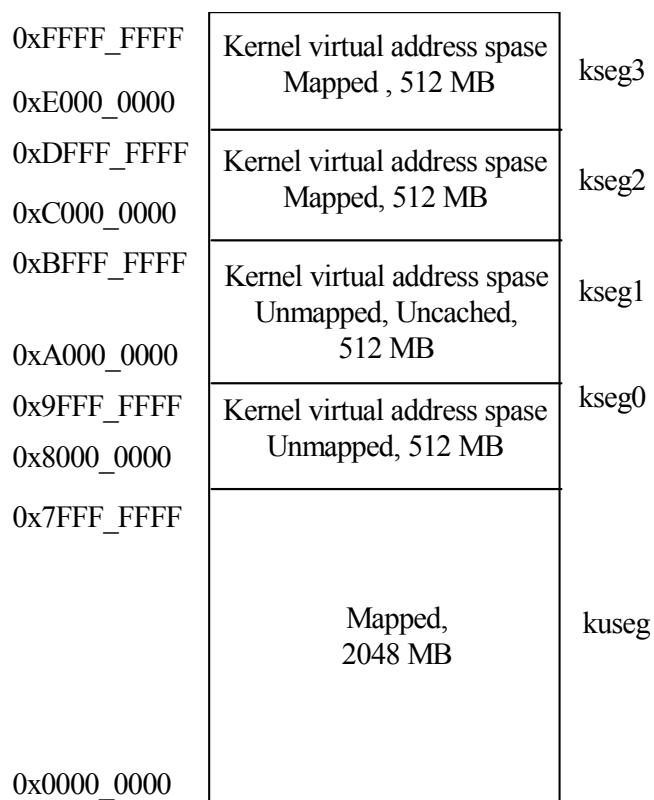

Виртуальные сегменты памяти, на которые делится адресное пространство, различаются в зависимости от режима работы процессора. На Рисунок 2.9 показана сегментация

для 4 Гбайт ( $2^{32}$  байт) виртуального адресного пространства, адресуемого 32-разрядным виртуальным адресом для обоих режимов работы.

Ядро входит в режим Kernel после аппаратного сброса или когда происходит исключение. В режиме Kernel программное обеспечение имеет доступ к полному адресному пространству и ко всем регистрам CP0. В режиме User доступ ограничен подмножеством виртуального адресного пространства (0x0000\_0000 - 0x7FFF\_FFFF) и запрещен доступ к функциям CP0. В режиме User недоступны виртуальные адреса 0x8000\_0000 - 0xFFFF\_FFFF и обращение к ним вызывает исключение.

Рисунок 2.9. Карта виртуальной памяти для режимов User и Kernel

Каждый из сегментов, показанных на Рисунок 2.9, является либо отображаемым (mapped), либо неотображаемым (unmapped). Различие объясняется в следующих двух разделах.

#### 2.5.2.1.1 Неотображаемые сегменты

В неотображаемом сегменте механизмы TLB или FM для преобразования виртуального адреса в физический адрес не используются. Особенно важно иметь неотображаемые сегменты памяти после аппаратного сброса, потому что TLB еще не запрограммировано и не может осуществлять преобразования.

Для неотображаемых сегментов преобразование виртуального адреса в физический является фиксированным.

Все неотображаемые сегменты, за исключением kseg0, никогда не кэшируются. Кэшируемость kseg0 определяется полем K0 регистра Config CP0.

### 2.5.2.1.2 Отображаемые сегменты

В отображаемом сегменте для преобразования виртуального адреса в физический адрес используются TLB или FM.

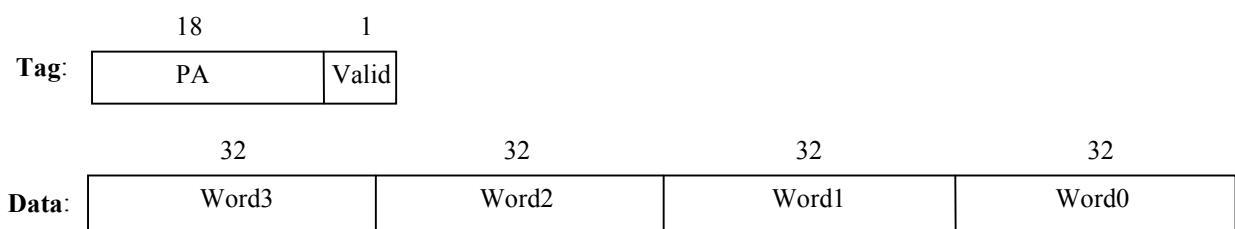

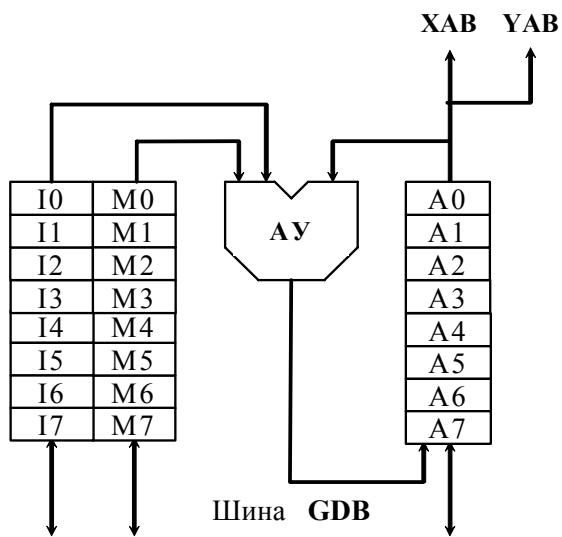

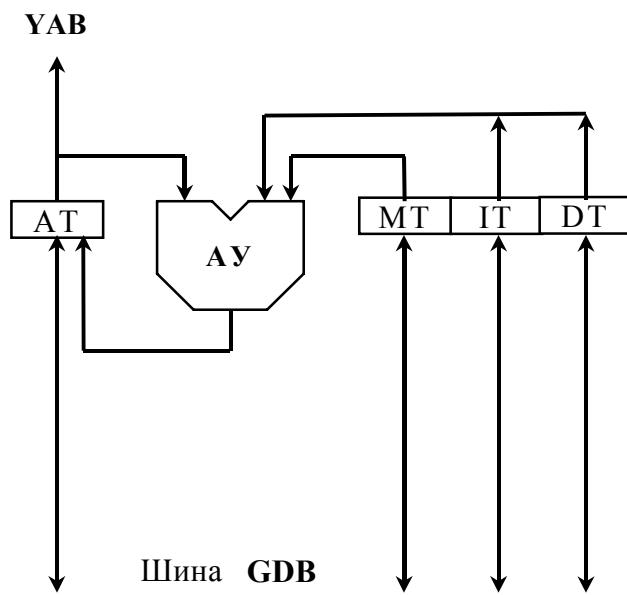

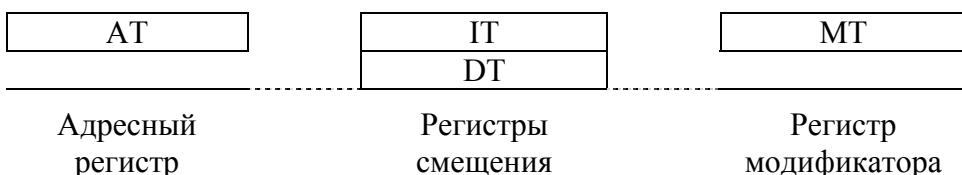

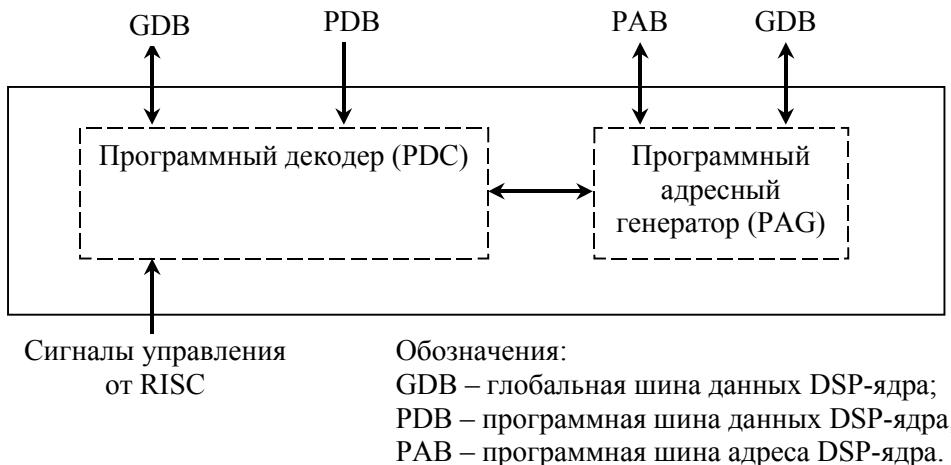

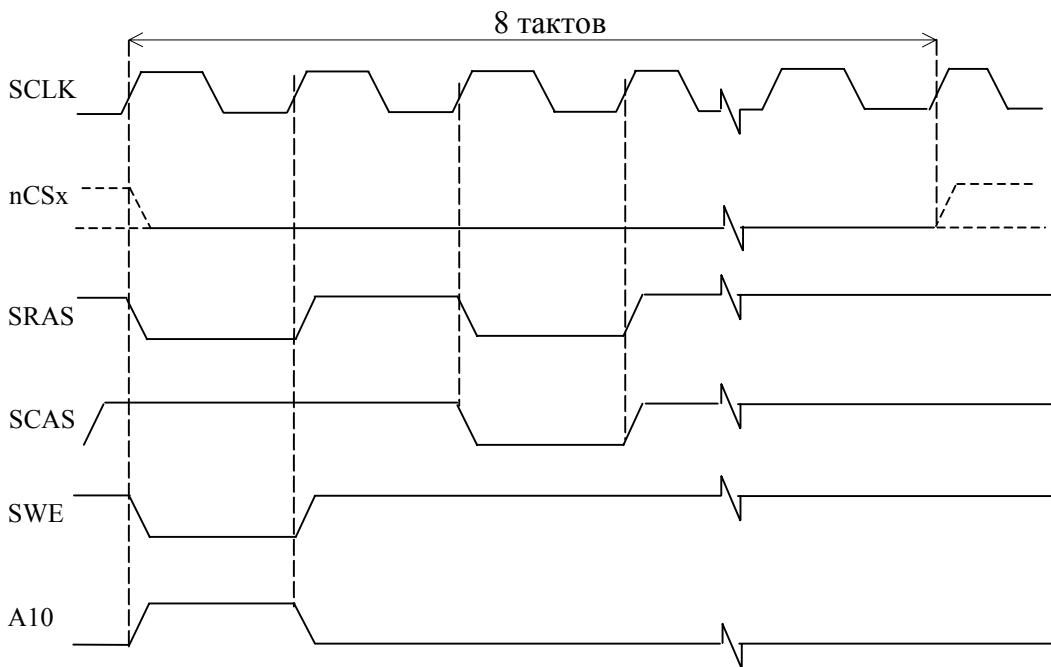

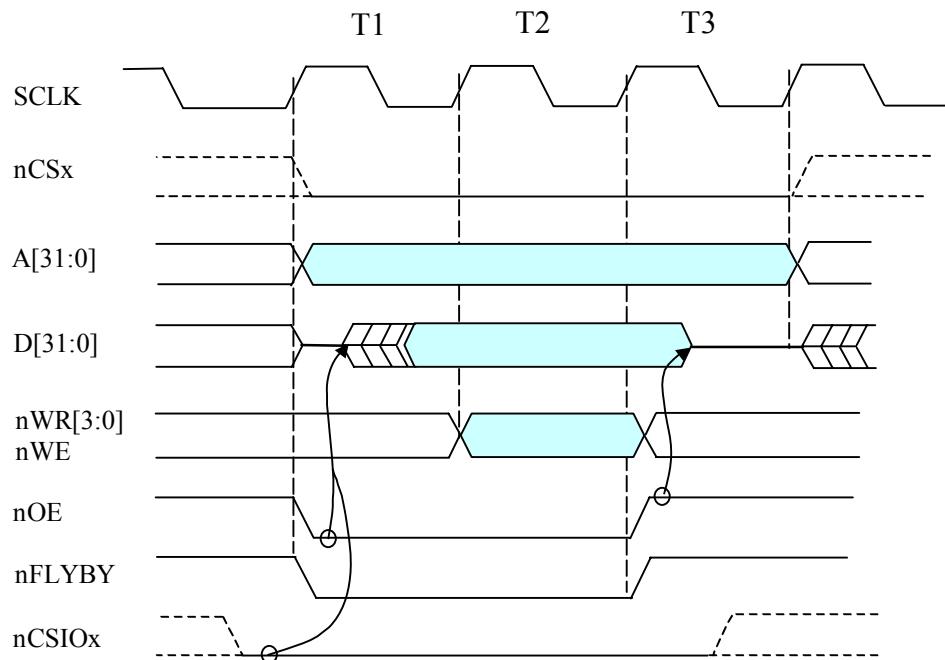

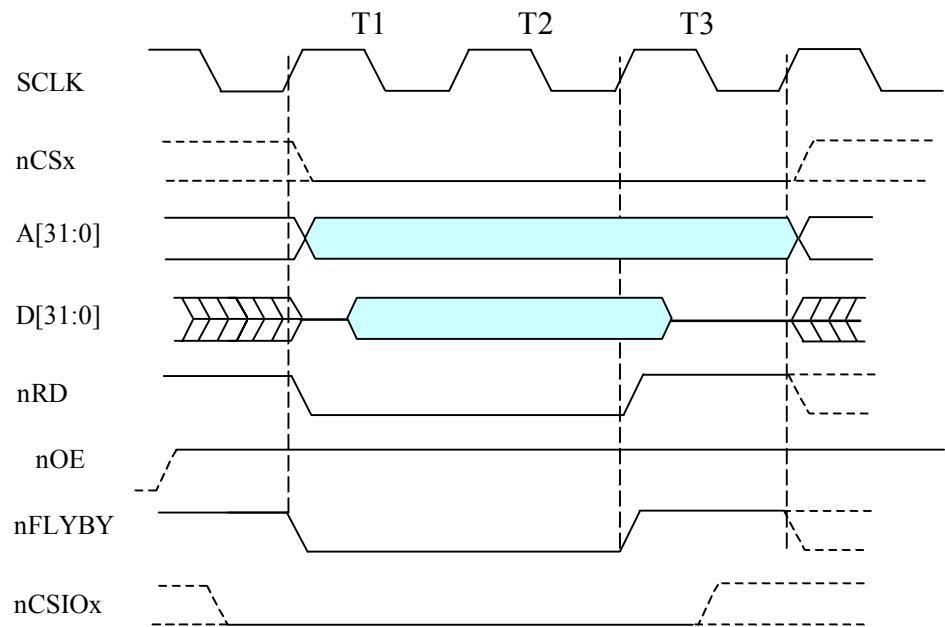

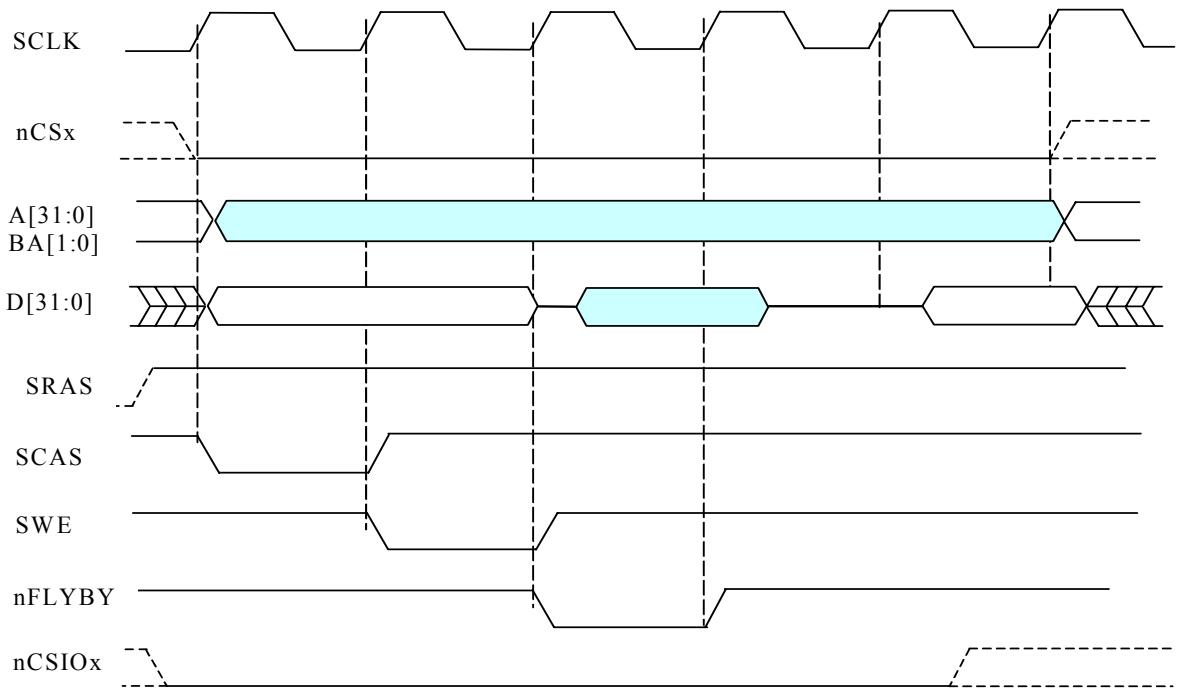

В режиме TLB преобразование отображаемых сегментов имеет постраничную основу. При преобразовании выявляется информация о кэшируемости страницы, а также атрибуты защиты, относящиеся к странице.